Vai trò của AI trong thiết kế chip ngày càng mở rộng, thu hút các công ty khởi nghiệp mới

Using AI in EDA is reinvigorating the whole tools industry, prompting established players to upgrade their tool offerings with AI/ML features, while drawing in startups trying to carve out differentiated approaches to fill unaddressed gaps with new tools and methodologies.

Today’s new generation of entrepreneurs is comprised of both young post-grads with innovative ideas and industry veterans taking a fresh look at old problems. The starting point for all of them is the software, drilling down into the challenges of specific applications or workloads and determining the best way to optimize hardware to meet those challenges.

“In general, AI technology/research is progressing fast, and faster than many established companies can keep up with,” said Chris Mueth, new opportunities business manager at Keysight Technologies. “Universities and startups are essential for investing in leading edge technologies that have a high-risk profile. Startups, by definition, are high risk with higher reward endeavors. To break into a market, they need to identify a key challenge, and take the risk to get out in front before any competitors. If successful, the industry responds, and everyone wins.”

Early EDA was driven by questions stemming from hardware designs, which led to the automation of complex, labor-intensive problems that continue to underpin Moore’s Law scaling in multiple dimensions. By contrast, AI is being added at a mature phase of EDA tool development, in which the innovations foster greater efficiencies and productivity for known processes and applications.

The result is a transitional moment, where everyone is pondering what comes next and where AI will work best. So far the future looks like an enhanced version of the present, with many technical challenges to be overcome, but that is likely to change in as-yet undefined ways.

“The chip design industry faces a wealth of demand, competition, and complex problems to solve,” said Tony Chan Carusone, CTO of Alphawave Semi. “AI can be a boon to the industry by enabling engineers to focus on innovating rather than on repetitive tasks. This shift will lead to the development of better, more efficient products with reduced risk.”

Much of the activity to augment EDA tools with AI stems from the expectation that in contrast to other industries, where workers fear AI taking their jobs, overworked chip design and verification engineers will welcome the help. “EDA AI will take away a lot of the busy work that engineers don’t like today, and take out a lot of the guesswork involved in design,” said Neil Hand, director of strategy for IC Verification Solutions at Siemens EDA. “AI also will allow us to continue to innovate at the pace needed, since there are simply not enough engineers to meet demand. It doesn’t fundamentally change the skillset of the engineers. It will just allow them to spend more time on innovation.”

To really move the needle, the EDA tools industry should prioritize reducing chip design cycle time, noted Kartik Hegde, co-founder and CEO at ChipStack. “It’s not acceptable that designing a chip today takes two to three years with hundreds of people. We need two orders of magnitude of reduction. Our North Star should be less than a month, less than 10 people. That will increase innovation.”

A new, AI-based approach in EDA should also reduce the tediousness of certain design tasks. “When I was a CTO, my heart bled every time I had my senior engineers writing basic old scripts to feed a new netlist into a future combiner,” said Pierre-Emmanuel Gaillardon, chief strategy officer at PrimisAI. “You want to re-use as much as possible. That’s what these tools can help you do. That’s how you solve this problem. You create productivity.”

EDA AI can help more pieces shift left. “We need to have design stages actually overlap with each other, where you’re doing front-end while you’re doing back-end design,” said Akash Levy, co-founder and CTO at Silimate. “The real key is to give insights early, and then take it through to the end of the process quickly. That also means giving engineers information that they would otherwise need to wait on for three months or more.”

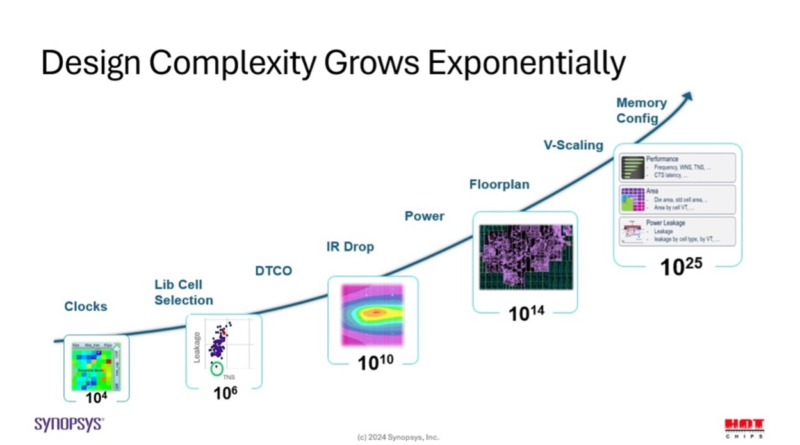

Stelios Diamantidis, distinguished architect and head of Synopsys’ Generative AI Center of Excellence, said in his presentation at this year’s Hot Chips conference that the design space is so enormous that it’s hard to identify causal relationships, which increases the time and cost of solving issues. Thus, another goal is to have AI help reduce these overwhelming tasks, thereby increasing productivity and reducing costs.

“If you think about chip design flows, we’ve been bringing in AI technology that has been helping us with optimization, using reinforcement learning to help us get to solutions faster and with less effort,” Diamantidis said in an interview. “Generative AI augments that. It helps with bringing up new talent. It helps us get to information faster. It helps to train people and share across the team through turning user interfaces into natural language interfaces.”

Fig. 1: Design complexity increases the need for AI-enhanced tools. Source: Synopsys/Hot Chips

AI also helps ensure that what gets designed will actually work. “You have to get it right before you send it out,” said ChipStack’s Hegde. “Because of that, there is incredible obsession about 100% coverage. The state space is ridiculous. You cannot possibly verify everything. So how do you figure out the key things to verify? Because we have natural language understanding with these models, you can bring out information easily in an automated way to figure out what matters. That’s a key piece of reducing the time apart from faster iterations.”

Siemens’ Hand agrees that AI will be significant in verification and shift left. “On the traditional approaches to verification, AI will help answer the questions of what I need to test, and what I have not tested. This goes beyond coverage, which has the significant limitation of only measuring what you think to measure. For shift left we can leverage AI to give early guidance in the design process on workloads, requirements, modeling, etc. So rather than a disconnected flow, we now have a connected approach from ideation through implementation using an AI-enabled digital twin of the design.”

In practical terms, this means most of the current EDA startup projects focus on natural language-based AI copilots that can quickly translate English instructions into usable code faster and more accurately than general-purpose generative AI, and with a greater degree of interactivity.

Gaillardon said much of the feedback he gets comes from people who mistake what they’re doing for RTL generation. “It’s not about generation. It’s about deep links going both ways between RTL and other languages, then back to English, which helps designers have a deeper understanding of their system.”

Generative AI-based design assistants

AI copilots are part of a class of generative AI-based design assistants, which also includes chatbots that provide technical guidance, such as code analysis and verification summaries. Copilots function as AI-based code completion tools, with more advanced approaches enabling interactive suggestions. Google Trends shows the term “AI copilot” first peaked in late June 2021, shortly after GitHub announced its GitHub Copilot, built on work originally done for Microsoft’s Visual Studio. It has become a template for other, similar tools.

For example, Synopsys.ai Copilot integrates Microsoft’s Azure OpenAI Service to provide natural language conversational intelligence to design teams across all stages of chip design. There is already an interest among developers to see the performance and helpfulness of GithHub Copilot improved, leaving room for both startups and incumbents to offer better solutions.

Looking ahead, some researchers are considering the idea of creating natural language conversion assistants that could operate in languages beyond just English. One essential element for all of this work is the need for standards to avoid the cumbersome additional work of developing middleware for interoperability.

Potential stumbling blocks

According to Steve Roddy, chief marketing officer at Quadric, there are stumbling blocks that new roles for AI in EDA could run into, aside from the tremendous overhead of time and talent. “At first glance, EDA tools — especially synthesis, placement and routing and logic verification — seem like obvious candidates to greatly benefit from AI techniques. An EDA tool that bakes in AI-powered algorithms for placement of logic cells, based on prior experience with thousands of previous designs, is very likely to converge far more quickly on an acceptable layout/placement compared to starting from first principles each time. But the key question is what data is used to train that AI and who owns the data. Does the big semi company with hundreds of prior designs keep its data private and use that to enhance its physical design process only, leaving the competing startup further in the dust? Or does the EDA company have rights to ‘learn’ from thousands of prior customer designs and ‘transfer’ that know-how to other users? Similar questions can arise in using GenAI to write verification tests based on previous verification suites that AI has ‘seen’ before.”

Siemens’ Hand adds that the biggest challenge is agreement of data sharing, model training, and APIs. “This is something that Si2 is doing some work on, as well as Siemens. For EDA AI to be successful, it needs to be open, vendor-independent, and allow for safe exchange of data without exposing IP. Companies implementing closed solutions are going to be limiting what is possible — and more worrying — creating huge barriers to innovation.”

Moving beyond copilots

There is speculation as to whether copilots will continue to be the template for the future of AI EDA, or if completely novel EDA AI tools will upend the industry.

“The copilot is about making the user more effective and is going to be critical as we look at how we can make designers more effective by orders of magnitude,” said Hand. “There will, however, be new solutions that fundamentally change aspects of design and verification at every point along the flow. We have already seen glimpses of this in solutions, where they are changing what is verified and using AI to predict results, rather than just guiding the user.”

The startup community has a similar perspective. “We’re starting with the obvious — copilots, adding natural language on top of what we are doing,” said PrimisAI’s Gaillardon. “It’s completely greenfield, and we are going to find new interesting options to use these technologies to build on top of something to complement EDA. For example, workflow agents, working together toward verification and front-end design, and beyond that, completely different things that can tackle design challenges.”

Silimate’s Levy believes it’s going to start with copilots, which are like AI-assisted humans. “Then it will go the other way, to human-assisted AI. That’s where you have agents that can iterate on feedback from the tools, but you’re still interacting with EDA tools at the end of the day. It’s going to be agents that are able to communicate and do things together.”

To frame the current state-of-the-art, consider the Tesla Cybertruck. It may look like the embodiment of the chunky polygons of primitive video games, but its cartoon shape is an exploration of what vehicles, freed from the design constraints of accommodating internal combustion engines, potentially could be. In other words, in a new world, engineers’ imaginations could run wild.

“Right now, we’re in the Model S era,” said Gaillardon. “We can make really cool cars, but they’re all going to look like traditional cars. The next step is the Cybertruck. We’re not there yet.”

And as to where these startups fit in with existing tools and flows, at least from the perspective of PrimisAI, Gaillardon said, “The technology we designed sits on top of the giants. We’re not competing with them. We are using their technologies, our customers are using their technologies; we help do that better by creating a completely new type of field. That might lead to acquisition or that might lead to completely new rounds.”

Conclusion

EDA industry veteran Rick Carlson, now vice president of worldwide sales at Verific, reflected on the excitement driving both the startups and the stalwarts. “The industry has gone through various iterations. We’re in a totally new space where nobody is sure of exactly the outcome or the impact that AI is going to have on chip design. We know there are going to be some significant, major improvements in productivity, for just one example. Remember when the Go champion got beat? They said it wasn’t going to be possible. Then it happened. If you apply that analogy to our industry, I don’t want to miss this chapter. It’s going to be an amazing foundation.”

With or without AI assistance, it is important to be flexible in the era of the moving target. “The rate of change in AI networks is so extreme that using any form of hard-wired accelerator that supports a small subset of ML operators and a subset of ML network topologies found in today’s reference benchmarks virtually guarantees that by the time the chip comes back from the fab it is already obsolete,” Quadric’s Roddy said. “Accelerators paired with legacy programmable CPUs and DSPs is equally foolhardy because those types of architectures essentially plan on the accelerator becoming useless and the workload defaulting to running on the CPU, which means no ‘acceleration’ for new workloads. Full – and appropriate – programmability is the most likely path for success.”

In the end, it may turn out that AI in EDA is just a start on the industry’s many challenges. “Semiconductor is a relentless taskmaster with constantly increasing complexity, and 3D-IC is going to accelerate this even further,” Hand noted. “It isn’t just AI that needs new solutions to innovate. Many of the new ‘software-defined, silicon-enabled’ products need help. Many of these solutions will be AI-based. We can use AI to accelerate productivity. We can use AI to create new abstract models to accelerate design. We can use AI to bridge the many domains that now need to communicate. In many ways we are spoiled for choice, and this becomes a prioritization issue. Which EDA AI solutions will provide the greatest benefit, with the minimum disruption?”

Related Reading

Chip Design Digs Deeper Into AI

Collaborations are going wider and deeper with multi-chiplet designs.

Will AI Disrupt EDA?

It’s been decades since there was a disruption within EDA, but AI could change the semiconductor development flow and force changes in chip design.