Tunnelling-based ternary metal–oxide–semiconductor technology – Nature.com

Thank you for visiting nature.com. You are using a browser version with limited support for CSS. To obtain the best experience, we recommend you use a more up to date browser (or turn off compatibility mode in Internet Explorer). In the meantime, to ensure continued support, we are displaying the site without styles and JavaScript.

Advertisement

Nature Electronics volume 2, pages 307–312 (2019)

8700

78

59

Metrics details

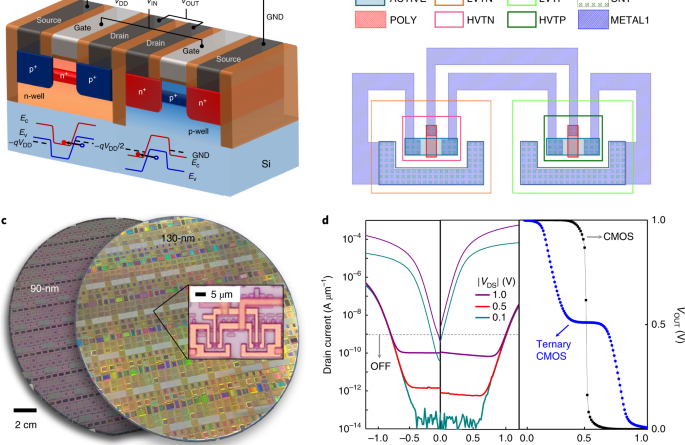

The power density limits of complementary metal–oxide–semiconductor (CMOS) technology could be overcome by moving from a binary to a ternary logic system. However, ternary devices are typically based on multi-threshold voltage schemes, which make the development of power-scalable and mass-producible ternary device platforms challenging. Here we report a wafer-scale and energy-efficient ternary CMOS technology. Our approach is based on a single threshold voltage and relies on a third voltage state created using an off-state constant current that originates from quantum-mechanical band-to-band tunnelling. This constant current can be scaled down to a sub-picoampere level under a low applied voltage of 0.5 V. Analysis of a ternary CMOS inverter illustrates the variation tolerance of the third intermediate output voltage state, and its symmetric in–out voltage-transfer characteristics allow integrated circuits with ternary logic and memory latch-cell functions to be demonstrated.

This is a preview of subscription content, access via your institution

Access Nature and 54 other Nature Portfolio journals

Get Nature+, our best-value online-access subscription

24,99 € / 30 days

cancel any time

Subscribe to this journal

Receive 12 digital issues and online access to articles

111,21 € per year

only 9,27 € per issue

Buy this article

Prices may be subject to local taxes which are calculated during checkout

The data that support the plots within this paper and other findings of this study are available from the corresponding author on reasonable request.

Moore, G. E. Cramming more components onto integrated circuits. Electronics 38, 114–117 (1965).

Google Scholar

Peercy, P. S. The drive to miniaturization. Nature 406, 1023–1026 (2000).

Article Google Scholar

Smith, K. C. The prospects for multivalued logic: a technology and applications view. IEEE Trans. Comput. C-30, 619–634 (1981).

Article MathSciNet Google Scholar

Hurst, S. L. Multiple-valued logic—its status and its future. IEEE Trans. Comput. C-33, 1160–1179 (1984).

Article Google Scholar

Esser, S. K. Convolutional networks for fast, energy-efficient neuromorphic computing. Proc. Natl Acad. Sci. USA 113, 11441–11446 (2016).

Article Google Scholar

Lennie, P. The cost of cortical computation. Curr. Biol. 13, 493–497 (2003).

Article Google Scholar

Merolla, P. A. et al. A million spiking-neuron integrated circuit with a scalable communication network and interface. Science 345, 668–672 (2014).

Article Google Scholar

Davies, M. et al. Loihi: a neuromorphic manycore processor with on-chip learning. IEEE Micro 38, 82–99 (2018).

Article Google Scholar

Mouftah, H. T. & Jordan, I. B. Design of ternary COS/MOS memory and sequential circuits. IEEE Trans. Comput. C-26, 281–288 (1977).

Article Google Scholar

Heung, A. & Mouftah, H. T. Depletion/enhancement CMOS for a lower power family of three-valued logic circuits. IEEE J. Solid-State Circuits 20, 609–616 (1985).

Article Google Scholar

Raychowdhury, A. & Roy, K. Carbon-nanotube-based voltage-mode multiple-valued logic design. IEEE Trans. Nanotechnol. 4, 168–179 (2005).

Article Google Scholar

Karmakar, S. Ternary logic gates using quantum dot gate FETs (QDGFETs). Silicon 6, 169–178 (2014).

Article Google Scholar

Shim, J. et al. Phosphorene/rhenium disulfide heterojunction-based negative differential resistance device for multi-valued logic. Nat. Commun. 7, 13413 (2016).

Article Google Scholar

Kim, Y. J. et al. Demonstration of complementary ternary graphene field-effect transistors. Sci. Rep. 6, 39353 (2016).

Article Google Scholar

Heo, S. et al. Ternary full adder using multi-threshold voltage graphene barristors. IEEE Electron Device Lett. 39, 1948–1951 (2018).

Article Google Scholar

Kane, E. O. Zener tunneling in semiconductors. J. Phys. Chem. Solids 12, 181–188 (1960).

Article Google Scholar

Taur, Y. & Ning, T. H. in Fundamentals of Modern VLSI Devices 2nd edn 125–126 (Cambridge Univ. Press, 2009).

Kim, K. R. et al. Silicon-based field-induced band-to-band tunneling effect transistor. IEEE Electron Device Lett. 25, 439–441 (2004).

Article Google Scholar

Ionescu, A. M. & Riel, Heike Tunnel field-effect transistors as energy-efficient electronic switches. Nature 479, 329–337 (2011).

Article Google Scholar

Sarkar, D. et al. A subthermionic tunnel field-effect transistor with an atomically thin channel. Nature 526, 91–95 (2015).

Article Google Scholar

Shin, S., Jang, E., Jeong, J. W., Park, B.-G. & Kim, K. R. Compact design of low power standard ternary inverter based on OFF-state current mechanism using nano-CMOS technology. IEEE Trans. Electron Devices 62, 2396–2403 (2015).

Article Google Scholar

Shin, S., Jang, E., Jeong, J. W. & Kim, K. R. In 2017 IEEE Int. Symp. Multi-Valued Logic (ISMVL) 284–289 (IEEE, 2017); https://doi.org/10.1109/ISMVL.2017.48

Taur, Y., Wann, C. H. & Frank, D. J. In 1998 IEEE Int. Electron Devices Meet. 789–792 (IEEE, 1998); https://doi.org/10.1109/IEDM.1998.746474

Borse, D. G. et al. Optimization and realization of sub-100-nm channel length single halo p-MOSFETs. IEEE Trans. Electron Devices 49, 1077–1079 (2002).

Article Google Scholar

Fujita, K. et al. In 2011 IEEE Int. Electron Devices Meet. 749–752 (IEEE, 2011); https://doi.org/10.1109/IEDM.2011.6131657

Zhang, X. et al. Comparison of SOI versus bulk FinFET technologies for 6T-SRAM voltage scaling at the 7-/8-nm node. IEEE Trans. Electron Devices 64, 329–332 (2017).

Article Google Scholar

Yoshitomi, T. et al. In 1993 Symp. VLSI Tech. 99–100 (IEEE, 1993); https://doi.org/10.1109/VLSIT.1993.760264

Toyoshima, Y., Eguchi, T., Hayashida, H. & Hashimoto, K. In 1991 Symp. VLSI Tech. 111–112 (IEEE, 1991); https://doi.org/10.1109/VLSIT.1991.706015

Pfiester, J. R. et al. An ultra-shallow buried-channel PMOST using boron penetration. IEEE Trans. Electron Devices 40, 207–213 (1993).

Article Google Scholar

Esseni, D. & Pala, M. G. Interface traps in InAs nanowire tunnel FETs and MOSFETs – part II: comparative analysis and trap induced variability. IEEE Trans. Electron Devices 60, 2802–2807 (2013).

Article Google Scholar

Park, B.-G., Hwang, S. W. & Park, Y. J. in Nanoelectronic Devices 222–223 (Pan Stanford Publishing, 2012).

Asenov, A. et al. Suppression of random dopant-induced threshold voltage fluctuations in sub-0.1-μm MOSFET’s with epitaxial and δ-doped channels. IEEE Trans. Electron Devices 46, 1718–1724 (1999).

Article Google Scholar

Taur, Y. et al. CMOS scaling into the nanometer regime. Proc. IEEE 85, 486–504 (1997).

Article Google Scholar

Bol, D., Ambroise, R., Flandre, D. & Legat, J. Interests and limitations of technology scaling for subthreshold logic. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 17, 1508–1519 (2009).

Article Google Scholar

Lewis, S. H., Fetterman, H. S., Gross, G. F., Ramachandran, R. & Viswanathan, T. R. A 10-b 20-Msample/s analog-to-digital converter. IEEE J. Solid-State Circuits 27, 351–358 (1992).

Article Google Scholar

Akopyan, F. et al. True north: design and tool flow of a 65 mW 1 million neuron programmable neurosynaptic chip. IEEE Trans. Comput. -Aided Des. Integr. Circuits Syst. 34, 1537–1557 (2015).

Article Google Scholar

Download references

This work was supported by the Samsung Research Funding & Incubation Center of Samsung Electronics under project number SRFC-TA1703-07 and by the U-K Brand Research Fund (1.180037.01) of UNIST (Ulsan National Institute of Science & Technology). The authors are grateful to foundry support for 130-nm and 90-nm CMOS technology processes.

Center for Nanoelectronic Brain-inspired Systems, Department of Electrical Engineering, Ulsan National Institute of Science and Technology, Ulsan, Republic of Korea

Jae Won Jeong, Young-Eun Choi, Woo-Seok Kim, Jee-Ho Park, Sunmean Kim, Sunhae Shin, Kyuho Lee, Jiwon Chang, Seong-Jin Kim & Kyung Rok Kim

You can also search for this author in PubMed Google Scholar

You can also search for this author in PubMed Google Scholar

You can also search for this author in PubMed Google Scholar

You can also search for this author in PubMed Google Scholar

You can also search for this author in PubMed Google Scholar

You can also search for this author in PubMed Google Scholar

You can also search for this author in PubMed Google Scholar

You can also search for this author in PubMed Google Scholar

You can also search for this author in PubMed Google Scholar

You can also search for this author in PubMed Google Scholar

K.R.K. conceived, planned and supervised the project. J.W.J. designed the layouts and foundry experiments, performed the device and circuit measurements and contributed to writing the initial draft of the manuscript. Y.-E.C. and W.-S.K. contributed to the measurements and simulations for experimental design. J.-H.P. and S.K. contributed to the circuit layout design. S.S. contributed to the initial design of the first foundry experiments and layouts. J.C. contributed to the device design, modelling and simulations. K.L. and S.-J.K. contributed to the circuit design and measurements. All authors discussed the results and wrote the manuscript.

Correspondence to Kyung Rok Kim.

The authors declare no competing interests.

Publisher’s note: Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Supplementary Figs. 1–7 and Supplementary Table 1.

Reprints and permissions

Jeong, J.W., Choi, YE., Kim, WS. et al. Tunnelling-based ternary metal–oxide–semiconductor technology. Nat Electron 2, 307–312 (2019). https://doi.org/10.1038/s41928-019-0272-8

Download citation

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1038/s41928-019-0272-8

Anyone you share the following link with will be able to read this content:

Sorry, a shareable link is not currently available for this article.

Provided by the Springer Nature SharedIt content-sharing initiative

Scientific Reports (2024)

Carbon Letters (2023)

Nature Communications (2022)

Scientific Reports (2022)

Nature Nanotechnology (2022)

Advertisement

© 2024 Springer Nature Limited

Sign up for the Nature Briefing newsletter — what matters in science, free to your inbox daily.