Tăng tính linh hoạt trong thiết kế với IP bộ xử lý dựa trên RISC-V

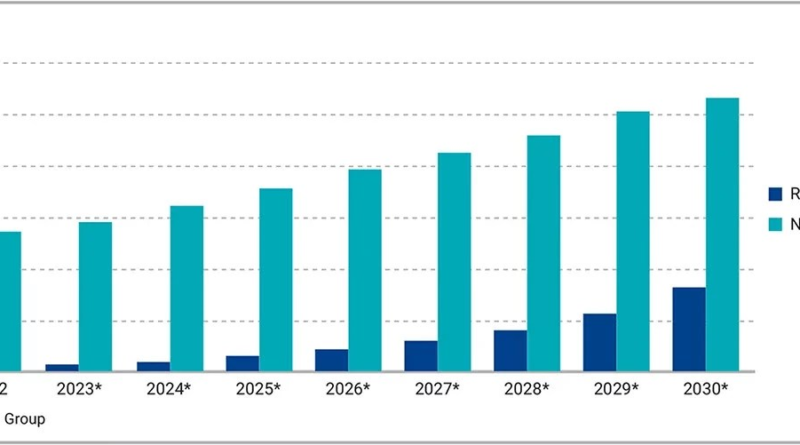

The semiconductor industry increasingly needs more flexible and scalable processor architectures, driving the growing adoption of RISC-V. Originally developed at the University of California, Berkeley, the open-source RISC-V instruction set architecture (ISA) has become very popular in recent years. RISC-V allows designers to customize their processor implementations to meet the specific needs of their target applications. By selecting the extensions they want to use for their design, developers can optimize for power, performance, and/or area (PPA). RISC-V also allows the addition of custom instructions, allowing designers to develop and add instructions for specific use cases, for example, AI or automotive, and differentiate their designs. Adoption by chip developers of the RISC-V architecture, with its openness, choices, and technical benefits, continues to accelerate. The SHD Group predicts a 40% compound annual growth rate (CAGR) for RISC-V-based SoCs from 2023 to 2030.

Fig. 1: >40% CAGR forecasted for SoCs with RISC-V processor.

Benefits of the RISC-V ISA

As an open standard instruction set architecture, RISC-V is defined by RISC-V International member companies. Through collaboration, these companies can contribute to new avenues of processor innovation while promoting new degrees of design freedom. Additionally, RISC-V isn’t bound by the constraints associated with proprietary ISAs, making it an attractive alternative for companies that are looking for greater flexibility.

The common ISA enables designers to use the same base ISA as a starting point and tailor their device to the needs of applications ranging from embedded designs to high-performance computing. This, combined with a strong and extensive software ecosystem, provides designers with a highly versatile option that can address the unique demands of a wide array of market segments. Rather than being locked into a limited set of development tools, designers have a broad and ever-expanding set of tools to choose from. The growing adoption of RISC-V, in turn, drives continued development of the ecosystem.

RISC-V-based Synopsys ARC-V processor IP

There are many RISC-V implementations available today, both as open-source cores and as commercial IP products. Synopsys, as a provider of high-quality processor IP, is contributing to the growth and adoption of RISC-V with the launch of the ARC-V RISC-V processor IP. Chip designers will gain a broader range of flexible, extensible processors from a provider with a decades-long track record for delivering and supporting PPA-efficient implementations and optimized software development tools and libraries.

The Synopsys ARC-V portfolio includes 32-bit and 64-bit processors, with high-performance, mid-range, and ultra-low-power families, as well as functional safety versions. As with ARC processors, the ARC-V processor IP allows designers to extend, accelerate, and differentiate their processor cores through the addition of custom extensions, enabling them to increase performance, reduce power consumption, and reduce code size.

Fig. 2: Synopsys ARC-V RISC-V processor IP families.

The RMX embedded, RHX real-time and RPX host processors address a wide range of applications across segments such as automotive, industrial, consumer, storage, and networking. Offering a broad range of processing solutions allows customers to address varying performance requirements and scalability.

One example of ARC-based differentiation leverages more than a decade of expertise delivering processor IP optimized for automotive safety. The safety enabled ARC-V “FS” processors are designed from the outset to achieve the highest levels of functional safety as defined by the ISO 26262 standard, both for the systematic development as well as providing hardware safety mechanisms to support ASIL B and ASIL D risk management levels. They are also compliant with practices defined by the ISO 21434 automotive cybersecurity standard. With the PPA and functional safety benefits ARC-V processors provide, along with Synopsys’ expertise in security and safety, automotive design teams have a robust foundation upon which to develop smarter, more autonomous systems for tomorrow’s vehicles.

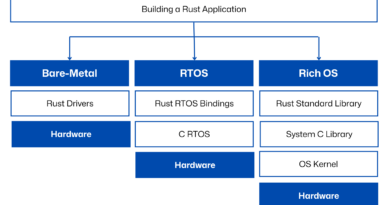

Synopsys ARC-V processors are supported by the growing RISC-V ecosystem, giving developers a menu of choices to build a flexible environment with all the required development tools. Synopsys’ embedded hardware and software partners provide development solutions for ARC processor-based systems across a wide array of market segments. The ARC-V processors are also supported by the commercial-quality ARC MetaWare Development Toolkit, which builds upon a 25-year legacy of providing complete solutions providing all the components needed to develop, debug and optimize embedded software.

Fig. 3: Synopsys MetaWare Development Toolkit components.

Conclusion

The flexibility, scalability and open architecture offered by the RISC-V ISA are major drivers of its success. RISC-V provides opportunities for innovation, giving SoC architects and software developers the ability to define new products and create a high degree of differentiation in their product portfolios. RISC-V will undoubtedly play a significant role in driving the future development of more innovative and efficient chips as the RISC-V ecosystem matures. With Synopsys ARC-V Processor IP, customers will benefit from optimized and configurable implementations and the flexibility to leverage this extensive RISC-V ecosystem, which will help achieve their IC design goals and accelerate time to market. For more information, visit: Synopsys ARC-V Processor IP.

Rich Collins

Rich Collins is the product marketing manager for IP subsystems at Synopsys. In this role, he is responsible for developing strategies and positioning for market penetration and growth of ARC processors and ARC-based subsystems within the DesignWare IP portfolio. Rich is an industry veteran with over 20 years of experience in embedded semiconductor R&D, product marketing and business development. Before joining Synopsys, he spent 17 years at Motorola/Freescale, where he held several technical and managerial roles within CPU, IP and SoC design and marketing teams across the company. Rich holds an MBA from Duke University’s Fuqua School of Business as well as a BSE in Electrical Engineering from Duke University, where he also majored in Computer Science and Spanish.