Tại sao các nhà thiết kế SoC cần Công cụ danh mục IP bán dẫn chuyên dụng

Semiconductor intellectual property (IP) management, reuse, and change tracking are essential for efficiently creating chip designs based on proven building blocks, reducing your time-to-market, and maintaining good reputations throughout their lifetimes.

Unfortunately, many SoC teams attempt to use existing tools like Git for these essential tasks, even though they are unsuitable and inconvenient in the long term.

In this article, understand the need for, and essential features of, semiconductor IP catalogs and their critical role in IP management and tracking. Also, discover how they facilitate semiconductor IP reuse.

What is semiconductor design IP management?

Design IP management involves the systematic search, details lookup, suitability analysis, usage tracking, dependency tracking, and change handling of all the semiconductor IP cores used or created during the product lifecycle of an integrated circuit (IC) or SoC.

What are IP cores?

IP cores are the building blocks of an SoC or IC design. Each IP core is a standalone semiconductor module that encapsulates a set of functionalities of the SoC or IC.

Some common examples of general-purpose IP cores include:

- central processing units (CPUs) like the advanced reduced instruction set computing machine (ARM) cores or the royalty-free RISC-V cores

- key computing subsystems like memory controllers

- analog and mixed-signal processing cores that function as analog-to-digital converters, digital-to-analog converters (DACs), analog filters, phase-locked loops (PLLs), or power management ICs

- digital signal processing (DSP) cores

- peripheral interface IP cores that implement the physical (PHY) and higher layer encoder-decoder functions for connectivity standards like Ethernet, Bluetooth, mobile industry processor interface (MIPI), peripheral component interconnect (PCI), PCI Express (PCIe), and others

Some examples of IP cores for application-specific ICs (ASIC) include:

- SerDes PHY receivers for automotive in-vehicle networking

- vertical-cavity surface-emitting laser (VCSEL) chips for high-speed high-bandwidth data center optical links

- 5G transceiver cores for industrial internet of things (IoT) automation

The importance of IP cores in design IP management

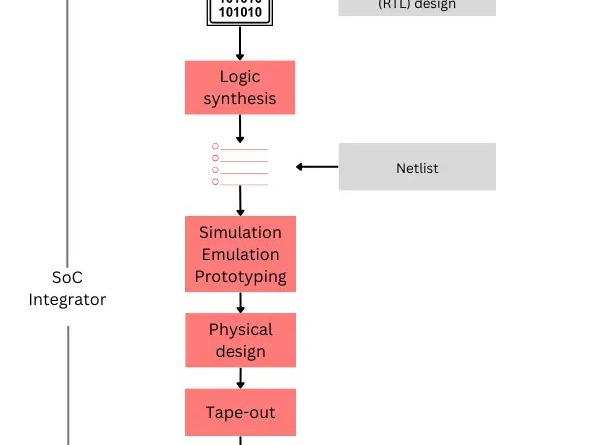

Fig. 1: IP cores in traditional SoC design.

In traditional SoC designs, IP cores are used as follows:

- The constituent IP cores are integrated through a communication bus or a network-on-chip.

- This integration is described by a single register transfer level (RTL) design. SoC engineers prefer soft IP cores for their flexibility as they are described by high-level RTL designs that can be modified and synthesized to suit the SoC’s process technology, power, and performance targets. In contrast, hard IP cores are only available as unmodifiable, process-specific, physical layout files, which makes them much harder to integrate into an SoC.

- The RTL design then undergoes a logic synthesis step to derive a netlist.

- This netlist is optimized for the chosen process technology while satisfying timing, area, and power constraints.

This implies that all the selected IP cores must be compatible with that process technology from the start. The original IP cores are modified and adapted for the selected process technology in the synthesis step by the system integrator company. All this adaptation followed by verification can be quite time-consuming and inefficient for fast-moving industries like consumer electronics.

Fig. 2: IP cores in chiplet SoC design.

To address such shortcomings, the semiconductor industry has been evolving toward using chiplets for SoC designs. The key difference of this approach is that the chiplets of an SoC can follow different process technologies. So the chiplets can be independently designed by domain-specialist IP vendors using any process technology and integrated faster without an RTL step as long as it conforms to one of the chiplet communication standards (like the chip-on-wafer-on-substrate interface or the universal chiplet interconnect express).

What does all this mean for design IP management? These processes place the following requirements on an SoC integrator’s IP management methodology:

- The process technology, chiplet interface (if chiplet-based), timing, area, and power requirements of each IP core must be available to the SoC designers.

- They must be able to search for candidate IP cores and match them with one another by analyzing their compatibility.

Challenges in design IP management and reuse

Some key challenges of IP management are outlined below:

- Choosing appropriate IP: Selecting IP cores to match technology processes and other constraints is time-consuming. It involves detailed assessments of design requirements, IP quality, licensing, and performance. More often than not, engineers in different business units are not aware of the IP cores that have been developed by other units.

- Incorporating IP: Integrating diverse internal and third-party IP cores requires significant effort to ensure performance and compatibility. Compatibility issues can delay projects and increase costs.

- Validating IP: Extensive simulations and verification are necessary to qualify the integrated IP blocks. Detailed records of verifications must be maintained for internal and regulatory compliance.

- Monitoring IP: Accurate monitoring of version updates, deployment efforts, and licensing is crucial to prevent violations and ensure compliance with relevant International Organization for Standardization (ISO) standards. Information silos and lack of automation complicate this process.

- Maintaining compliance: Increasing IC complexity makes meeting industry standards tougher. Maintaining design traceability is critical for compliance with regulations like export restrictions and standards like ISO 26262 for automotive functional safety.

- Protecting IP: Safeguarding IP is vital for competitive advantage and regulatory compliance. Risks of leakage can have legal and business repercussions. Strong security measures like encryption, access controls, and regular audits are necessary.

- Supporting multi-site collaboration: Facilitating multi-site collaboration and knowledge exchange requires seamless access to shared IP knowledge, advanced permission controls, integrated data flows, and economical network storage solutions.

Apart from the above general challenges of IP management, effective semiconductor IP reuse involves some additional challenges:

- Tracking IP efficiently: For faster time-to-market, SoC integrators prefer to license proven IP cores from specialist companies or outsource the designs. They would love to integrate these designs as quickly as possible. However, both licensing and outsourcing involve tracking a lot of IP from a large number of suppliers, leading to tracking problems, compliance issues, and access issues across different teams.

- Avoiding duplication of effort: Poor IP reuse and management may result in duplicated efforts to create common designs.

- Ensuring quality: Reluctance to adopt third-party IP arises from unverified quality and limited lifecycle visibility, affecting productivity and reliable IP reuse.

- Handling lack of standardization: Lack of standardized IP specifications and proper documentation complicates IP evaluation and integration. Without systematic cataloging, engineers are forced to try to manually and inefficiently infer IP core metadata from raw simulation and analytics reports and through dozens of back-and-forth emails with coworkers.

- Understanding licensing issues: Unwitting license violations can lead to liabilities. Ensuring consistent use and timely updates of IP versions is crucial to avoid compliance issues.

- Solving compatibility concerns: Reusing existing IPs complicates system integration because it requires thorough IP understanding and interface design, increasing design overhead. Managing resources in hierarchical IP reuse is also challenging.

What is a semiconductor IP catalog, and how does it improve design IP management?

An IP catalog is a centralized digital repository with detailed information about all the semiconductor IP blocks being used and available for use in an organization. It contains comprehensive details about every internal and third-party IP block:

- detailed metadata, including information about the foundry and technology node

- files created by chip design tools and electronic design automation (EDA) software

- design-related metrics and documentation

- verification-related knowledge

- IP core dependency information

- standards certifications

- licensing details and agreements

For IP development of new designs by an organization for internal use or external partners, the IP catalog can also store proprietary information like:

- configurations and device models for emulators

- code and data for prototyping the design using, for example, a field-programmable gate array (FPGA)

- manufacturing-related information like the RTL descriptions, netlists, floorplans, design rule checks, and other verifications

The semiconductor IP catalog is at the heart of efficient semiconductor intellectual property management. It helps to achieve several positive outcomes like:

- enabling design teams to search, compare, track, and manage IPs, both internal and third-party

- detecting changes in constituent IP core versions throughout the engineering lifecycle of an SoC or IC

- facilitating enterprise-wide semiconductor IP reuse across teams and sites

- streamlining chip design data management and storage for efficient enterprise-wide access

From the organization’s point of view, the semiconductor IP catalog breaks down silos by offering centralized repositories. This in turn promotes more collaboration among design engineers across teams and sites since they’re all able to access the same information about a design.

Lastly, since the semiconductor IP catalog manages information for the entire lifecycle of an IC or SoC, it serves as the organizational memory about the IC design. Its information persists even as teams and roles change over time. If design bugs are found decades later, the engineers at the time can dive into the design’s history recorded in the catalog. They can trace the technical and business decisions that resulted in the bug and design suitable workarounds.

Why traditional and retrofit approaches to IP management fail

Fig. 3: Storage capacity required for design data.

Many semiconductor companies have attempted to retrofit existing software systems to implement semiconductor IP catalogs. Such software systems include:

- Git, a version control tool to manage software code, for tracking changes in IP core design files

- Confluence or similar document management systems for storing design data and documentation about IP cores

Another traditional approach, followed by some companies, is to rapidly develop rudimentary in-house tools specifically for IP management.

However, all these approaches have many shortcomings:

- Poor cataloging and search capabilities: These tools were not built for scale. They are incapable of efficiently cataloging and searching an organization’s entire IP portfolio, which may be in the thousands.

- Missing hierarchy and dependency management: Version control tools treat each code file as an independent unit without any dependency tracking between files. In contrast, chip design involves a multi-level dependency hierarchy of IP cores. If a heavily reused IP core changes, those changes must bubble up through all the cores above it in the hierarchy, triggering regression tests and other verifications for each affected core. Additionally, the changes must bubble up to all the projects that depend on that core at any level. Such change propagation is just not built into tools like Git.

- Lack of design tool integration: Existing and in-house tools often lack integration with the EDA and other design tools that the design engineers are using. This leads to workflow inefficiencies and design inconsistencies.

- Inability to handle large files: Typical data capacity requirements for chip design workflows range from hundreds of gigabytes to a few terabytes, as shown in the illustration above. Git is just not designed to efficiently store such large files.

- Unsuitability for binary design files: Another limitation of tools like Git is their clumsiness with binary formats. Most chip design data consists of binary format files. Understanding and visualizing any changes to them is essential, but Git isn’t capable of that. Minor changes in a binary file can’t be incrementally updated, forcing the entire file to be re-uploaded.

- Inconsistent versions: Although Git is a distributed version control system, its sync workflows are inconvenient for users and inefficient with the large binary files prevalent in chip design. So different teams may end up working on different versions of the chip design files, resulting in inconsistencies and compatibility errors at tape out.

- Problems with IP security: These tools are not suitable for access control that is both fine-grained and domain-aware. For example, you may want to ensure that a layout engineer doesn’t change a schematic and prevent contractors from accessing sensitive design libraries. This kind of nuanced access control isn’t easy with such tools.

- Unawareness about legal conditions: These tools don’t facilitate compliance with licensing and usage restrictions.

Why a purpose-built semiconductor IP catalog is the right solution

Purpose-built solutions for chip design data and IP management that are architected from scratch specifically for chip design use cases are essential for your SoC engineers. They can scale up to enterprise-wide usage and enhance your return on investment.

Their benefits include:

- Accurate searching and matching: IP core search and match helps engineers locate and compare all the IP available across the enterprise — whether third-party or internal — throughout the engineering lifecycle. Though different business units may work like knowledge silos, the systematic publishing of all IP cores to a central catalog with standardized metadata enables engineers across business units to be aware of each others’ IP designs and reuse them.

- Hierarchy awareness: These tools automatically identify IP dependencies and track IP usage across an enterprise. Whenever an IP core changes, they trigger automated actions for all affected cores. They are aware of chip design complexity.

- Native integration with EDA tools: As soon as a change is done from an EDA tool, those changes are automatically and efficiently propagated throughout the enterprise.

- Large binary file support: These tools can render file changes as visual changes in design diagrams. They enable engineers to access design data without downloading the entire set of large binary files to local workstations, which would be prohibitively slow and blow up network usage costs if any. Another benefit is their ability to upload incremental changes quickly without re-submitting entire files.

- Centralized repository for consistent views: By maintaining all the data centrally and downloading them to workstations efficiently, all users across the enterprise anywhere in the world see the same file data at all times.

- Secured IP: Purpose-built tools implement robust data security and access controls.

- Awareness of licensing and usage restrictions: These tools provide built-in support for storing and analyzing licensing terms and other legal requirements.

Case study: Reducing design time with IP management solutions

Allegro MicroSystems is a designer of automotive, industrial, and power management ICs. Before 2005, their IP management workflows faced challenges like:

- Siloed knowledge: Business units were using disparate systems to store their IP knowledge. This made searching inefficient and engineers unaware of potentially reusable designs from other units.

- Manual knowledge gathering: Engineers had to infer IP core metadata through simulation results, analytics reports, and time-consuming back-and-forth with coworkers.

- Traceability problems: The lack of systematic design traceability and automatic reporting processes complicated their compliance efforts.

By adopting Keysight HUB and SOS, all business units across Allegro could systematically publish their IP designs to the central IP catalog with standardized metadata. Other teams were able to easily search and retrieve IP metadata. Traceability and compliance improved due to HUB’s ability to track IP use across projects and business units.

Keysight HUB and SOS enable the enterprise-level tracking of over 200 IPs across 150 projects. Nearly 55% of Allegro’s IPs today are derived and modified from proven template IPs, enabling as much as 45%-50% reduction in design time, shorter engineering life cycles, and faster time-to-market.

Solutions for IP and design data management

Fig. 4: Compare IP cores in Keysight HUB.

Keysight HUB is our solution for semiconductor IP management. It provides all the benefits of the purpose-built solutions explained above. More specifically:

- It tracks IP and dependencies automatically.

- It allows searching for IP using a bill of materials and consumer filters to help guide the selection, updates, integration, and verification of IP cores.

- It provides clear design traceability of any silicon IP across the full hierarchy.

- Traceability also helps with managing engineering change orders.

Fig. 5: Keysight SOS for hierarchical IC design data management.

Keysight SOS is our feature-rich high-performance system for design data management. Together with HUB, it enables design teams to efficiently store and sync design data, track changes, automate traceability reporting, and collaborate with other teams in real time to solve any design problems.