Silicon Creations đang thúc đẩy chip thế hệ tiếp theo

![]()

Next generation semiconductor design puts new stress on traditionally low-key parts of the design process. One example is packaging, which used to be the clean-up spot at the end of the design. Thanks to chiplet-based design, package engineers are now rock stars. Analog design is another one of those disciplines.

Not long ago, analog design had a niche place in semiconductor design for the small but important part of the system that interfaced to the real world. Thanks to the performance demand of things like AI, analog design is now a critical enabling technology for just about every system. Data communication speed and latency as well as ubiquitous sensor arrays are prevalent in all advanced designs. These technologies now rely on analog design. At a recent Siemens event, substantial details were presented about this change in system design. Let’s dig into how Silicon Creations is fueling next generation chips.

The Event

Siemens EDA held its Custom IC Verification Forum recently on August 27 in Austin. The event aimed to present a comprehensive view of leading-edge AI-enabled design and verification solutions for custom ICs. Topics such as circuit simulation, mixed signal verification, nominal to high-sigma variation analysis, library characterization, and IP quality assurance were all covered.

You can check out more details about this event here. What you will see is most of the presentations are given by Siemens folks, with one exception. They keynote address is delivered by Silicon Creations. I’d like to cover the eye-opening insights presented in that keynote.

The Keynote

Randy Caplan, Principal and Co-Founder of Silicon Creations presented the keynote, entitled Increasing Analog Complexity is a Reality for Next Generation Chips. For nearly 18 years, Randy has helped to grow Silicon Creations into a leading semiconductor IP company with more than 450 customers in over 20 countries, with a remarkable statistic of nearly 100% employee retention.

Silicon Creations’ designs have been included in over 1,500 mass-produced chips from 2nm to 350nm, from which more than ten million wafers were shipped. The company is known for award-winning analog mixed-signal silicon intellectual property that lowers risk. You can learn about this unique company on SemiWiki here.

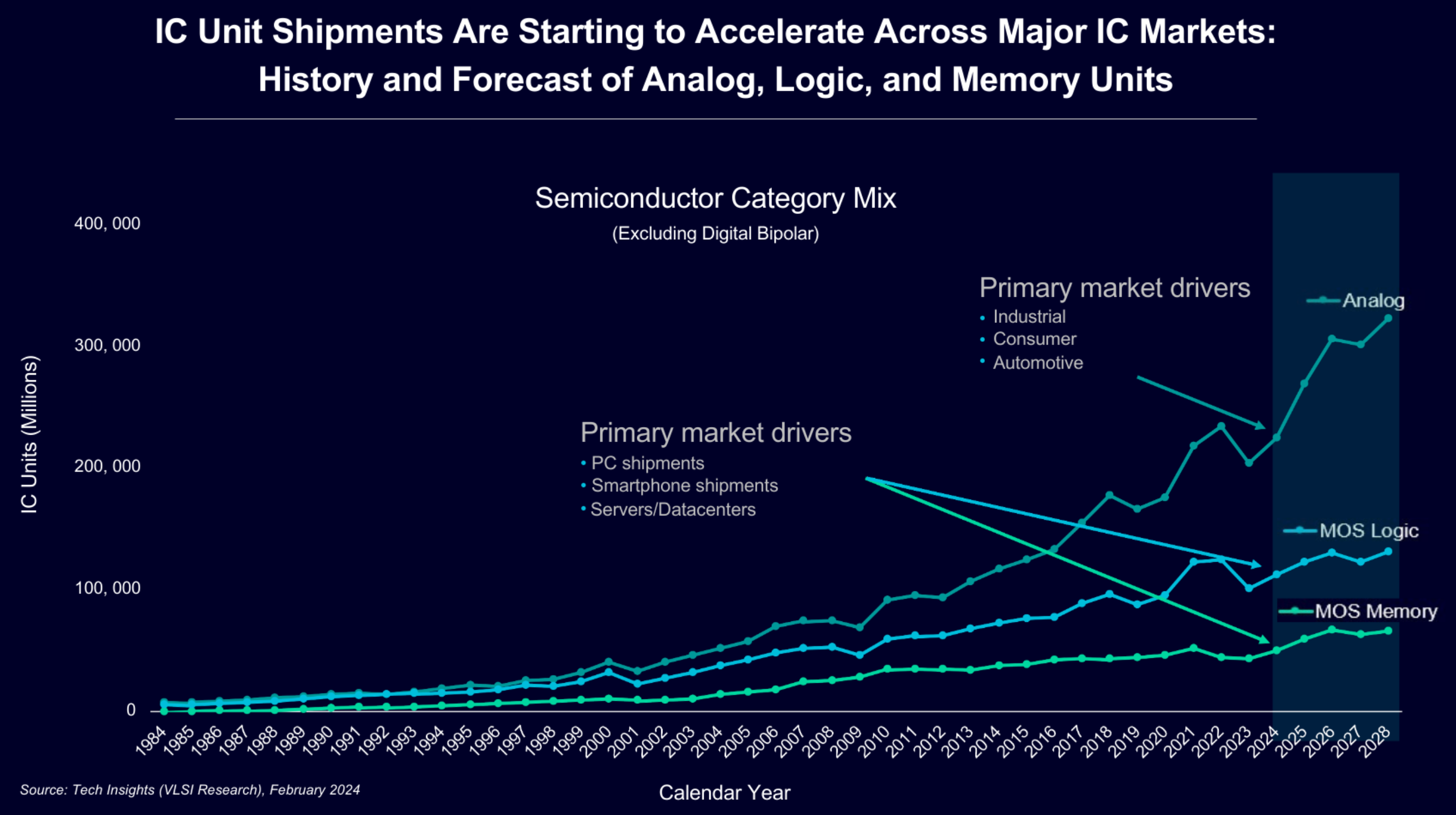

Randy’s keynote presented a great deal of information about how chip/system design is changing. He presented many trends, backed-up with detailed data to illustrate how growing complexity is enabled by high-performance analog IP. Below is one example that surprised me. We are all aware of the growth in MOS logic and memory. However, shipments of analog chips are actually growing much faster, indicates how ubiquitous analog IP is becoming across many markets.

Randy covered many other relevant and interesting topics in his keynote, including the evolution from monolithic to multi-die design, process technology evolution, multi-core trends, the growth of analog functions required for advanced designs, reliability considerations, and a broad overview of design and process challenges. The unique demands of SerDes and PLL design are also explored.

There are examples presented, along with several architectural options to consider. The collaboration between Silicon Creations and Siemens is discussed, along with details around the use of Siemens Solido, Calibre and Questa solutions are presented.

To Learn More

I have provided a high-level overview of the topics covered in Randy’s keynote. There is much more detail and many more insights available in the slides. If analog content is becoming more important to your chip projects, you should get your own copy of this important keynote address. You can download it here and learn more about how Silicon Creations is fueling next generation chips.

Share this post via: