Silicon Creations đang kích hoạt cuộc cách mạng Chiplet

![]()

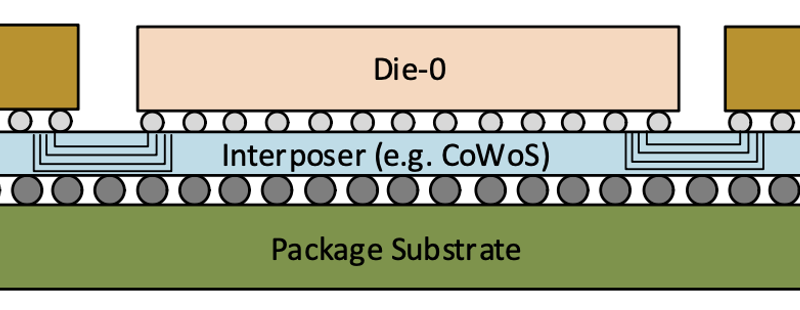

The multi-die chiplet-based revolution is upon us. The ecosystem will need to develop various standards and enabling IP to make the “mix and max” concept a reality. UCIe, or Universal Chip Interconnect express is an open, multi-protocol on-package die-to-die interconnect and protocol standard that promises to pave the way to a multi-vendor chiplet market. But delivering an implementation that balances all the requirements for power, performance and form factor can be quite challenging. At the recent IP-SoC Silicon Valley event, Silicon Creations presented a comprehensive strategy to overcome these challenges. Read on to see how Silicon Creations is enabling the chiplet revolution.

About Silicon Creations

Silicon Creations is a self-funded, leading silicon IP provider with development in the US and Poland, and a sales presence worldwide. The company provides world-class IP for precision and general-purpose timing (PLLs), oscillators, low-power, high-performance multi-protocol and targeted SerDes, and high-speed differential I/Os. Applications include smart phones, wearables, consumer devices, processors, network devices, automotive, IoT, and medical devices.

The majority of the world’s top 50 IC companies work with Silicon Creations. 1,000+ chips contain the company’s IP using over 700 unique IP products. Silicon Creations touches over 150 production tape-outs each year with over 400 customers, with 3nm designs in mass production. You can learn more about Silicon Creations at SemiWiki here.

About the Die-to-Die Interface Challenges

Blake Gray developed a comprehensive presentation for IP-SoC Silicon Valley. He is the Director of Hardware Engineering at Silicon Creations. He’s been with the company for over 12 years. Unfortunately, he fell ill before the event and Jeff Galloway, Principal and Co-Founder at Silicon Creations stepped in to present for Blake. Let’s take a look at the excellent material Blake developed. It begins with a discussion of the design and performance challenges of transmit (TX) clock design.

Clock performance is critical; it is distributed to all TX subcomponents. Furthermore, UCIe employs a two-phase feed-forward clocking architecture where timing jitter is between clock and data edges. Optimizing the TX clock design is a critical element for effective die-to-die communications. If the die-to-die interface becomes the performance bottleneck, the advantages of a chiplet design are potentially lost, so the stakes are high.

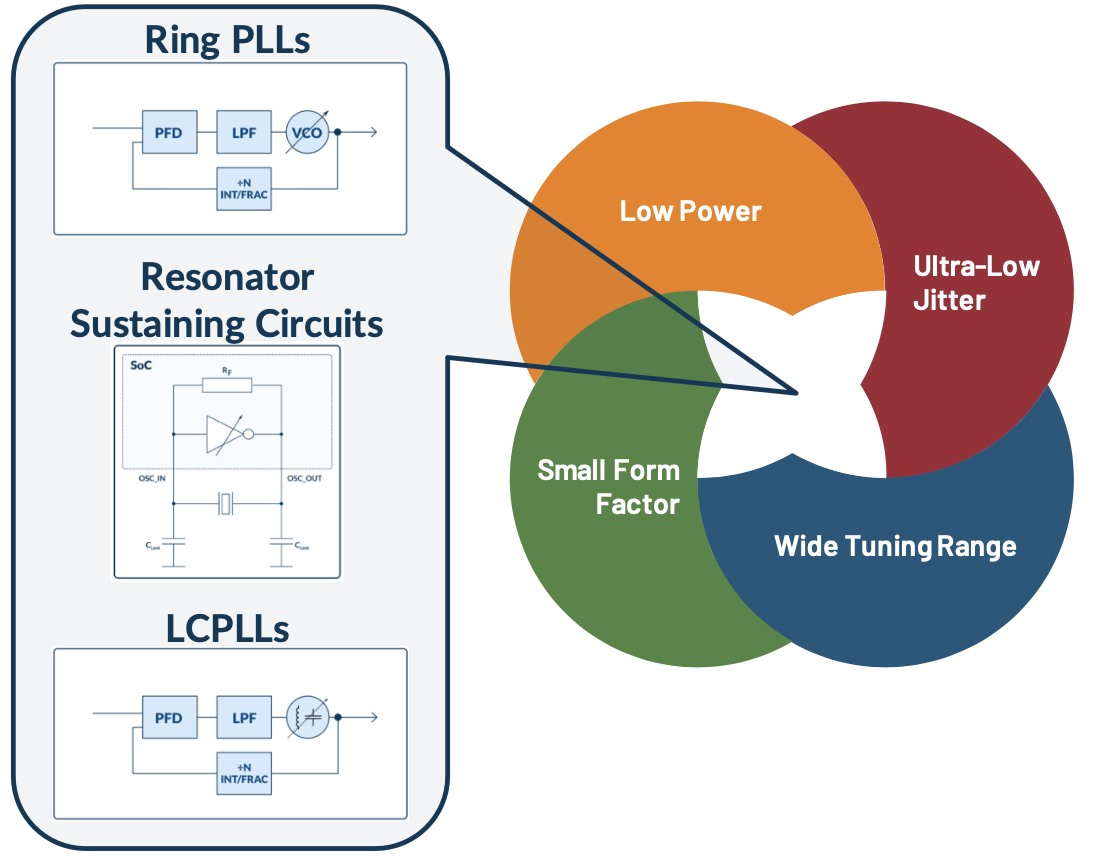

Next were the four competing requirements that must be balanced for a successful design – low power, small form factor, ultra-low jitter, and a wide tuning range. For this last point, a clocking solution with a wide tuning range is useful as it can support all data rates required with no need to integrate data rate-specific solutions per project. This makes the whole design effort easier and more reusable. The figure below illustrates these design challengers and some of the design solutions required.

The Silicon Creations Approach

The presentation then focused on some of the work going on at Silicon Creations to address these challenges. A dedicated die-to-die ring PLL was described that is currently in development on TSMC 7nm FF, but is easily portable to other process nodes. The PLL can be driven by any quality clock source, or even a resonator-based oscillator.

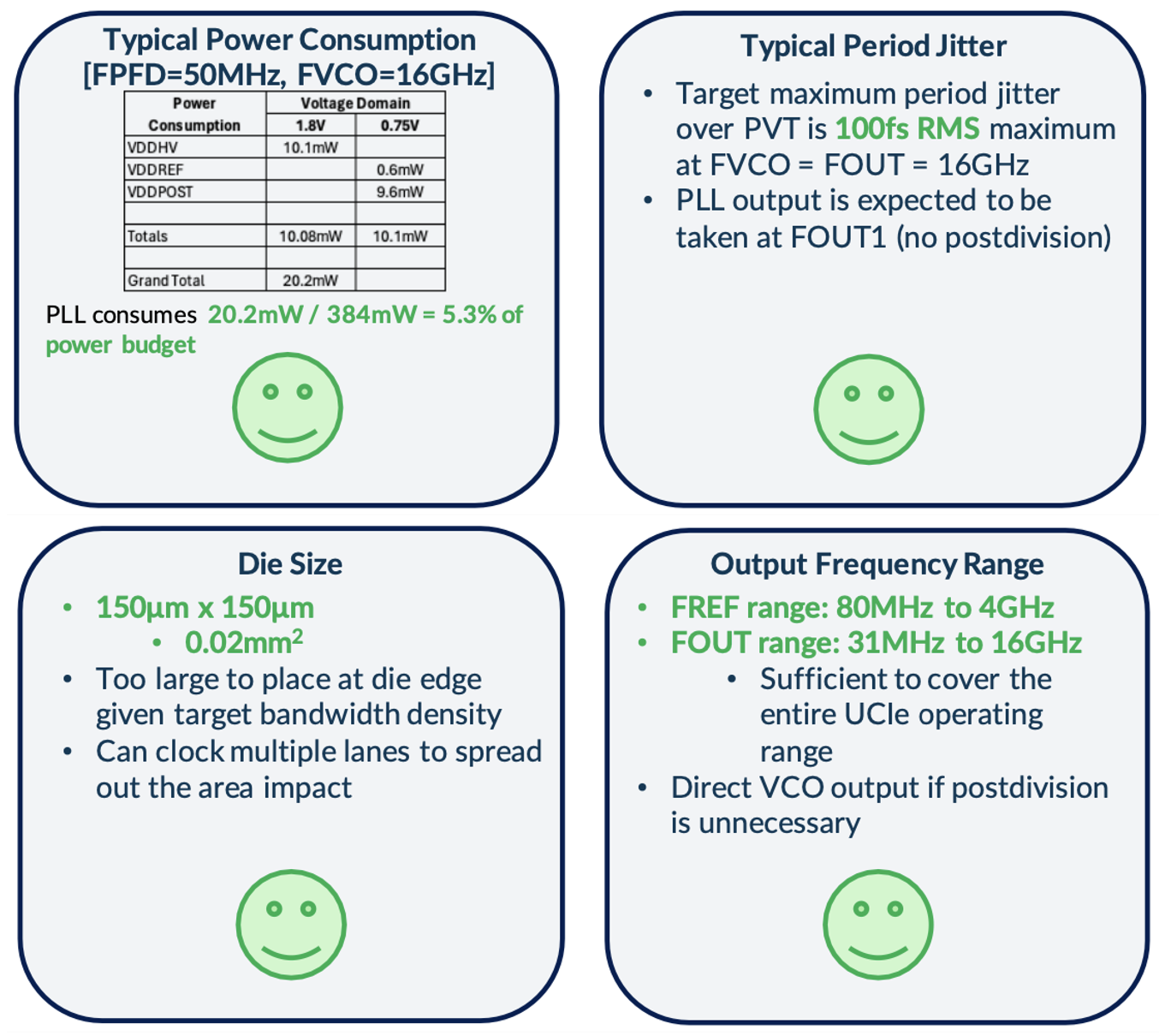

Applying this clocking solution for a standard package, 32GT/s application with a 16-bit data width results in a maximum power for the physical layer = 24mW x 16 = 384mW. More details on power consumption and other parameters are summarized in the diagram below.

Other die-to-die solutions also exist for TS16/12/6/5/4/3/2. The presentation concluded by stating that the immense performance requirements of clocking solutions (ultra-low jitter, low power, wide tuning range, and small form factor) mandate careful design considerations and optimization tradeoffs. The Silicon Creations clocking/XO sustaining circuit IP portfolio is well-positioned to meet the demands of designs requiring optimal die-to-die communications.

To Learn More

You can see the full line of high-performance IP available from Silicon Creations here. If you would like to reach out to the company to learn more, you can do that here. And that’s how Silicon Creations is enabling the chiplet revolution.

Share this post via: