Những cân nhắc quan trọng về thiết kế cho các kết nối chiplet băng thông cao (TSMC)

A new technical paper titled “High-Bandwidth Chiplet Interconnects for Advanced Packaging Technologies in AI/ML Applications: Challenges and Solutions” was published by researchers at TSMC.

Abstract:

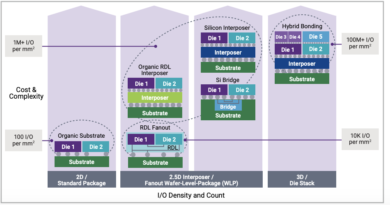

“The demand for chiplet integration using 2.5D and 3D advanced packaging technologies has surged, driven by the exponential growth in computing performance required by Artificial Intelligence and Machine Learning (AI/ML). This paper reviews these advanced packaging technologies and emphasizes critical design considerations for high-bandwidth chiplet interconnects, which are vital for efficient integration. We address challenges related to bandwidth density, energy efficiency, electromigration, power integrity, and signal integrity. To avoid power overhead, the chiplet interconnect architecture is designed to be as simple as possible, employing a parallel data bus with forwarded clocks. However, achieving high-yield manufacturing and robust performance still necessitates significant efforts in design and technology co-optimization. Despite these challenges, the semiconductor industry is poised for continued growth and innovation, driven by the possibilities unlocked by a robust chiplet ecosystem and novel 3D-IC design methodologies.”

Find the technical paper here. November 2024.

S. Li, M. -S. Lin, W. -C. Chen and C. -C. Tsai, “High-Bandwidth Chiplet Interconnects for Advanced Packaging Technologies in AI/ML Applications: Challenges and Solutions,” in IEEE Open Journal of the Solid-State Circuits Society, doi: 10.1109/OJSSCS.2024.3506694