[News] The Imminent Arrival of 2-Nanometer Advanced Process – TrendForce

Recently, IC design company Marvell announced an expansion of its long-term partnership with TSMC to include 2-nanometer technology. They will collaborate on developing the industry’s first 2-nanometer semiconductor production platform optimized for accelerating infrastructure.

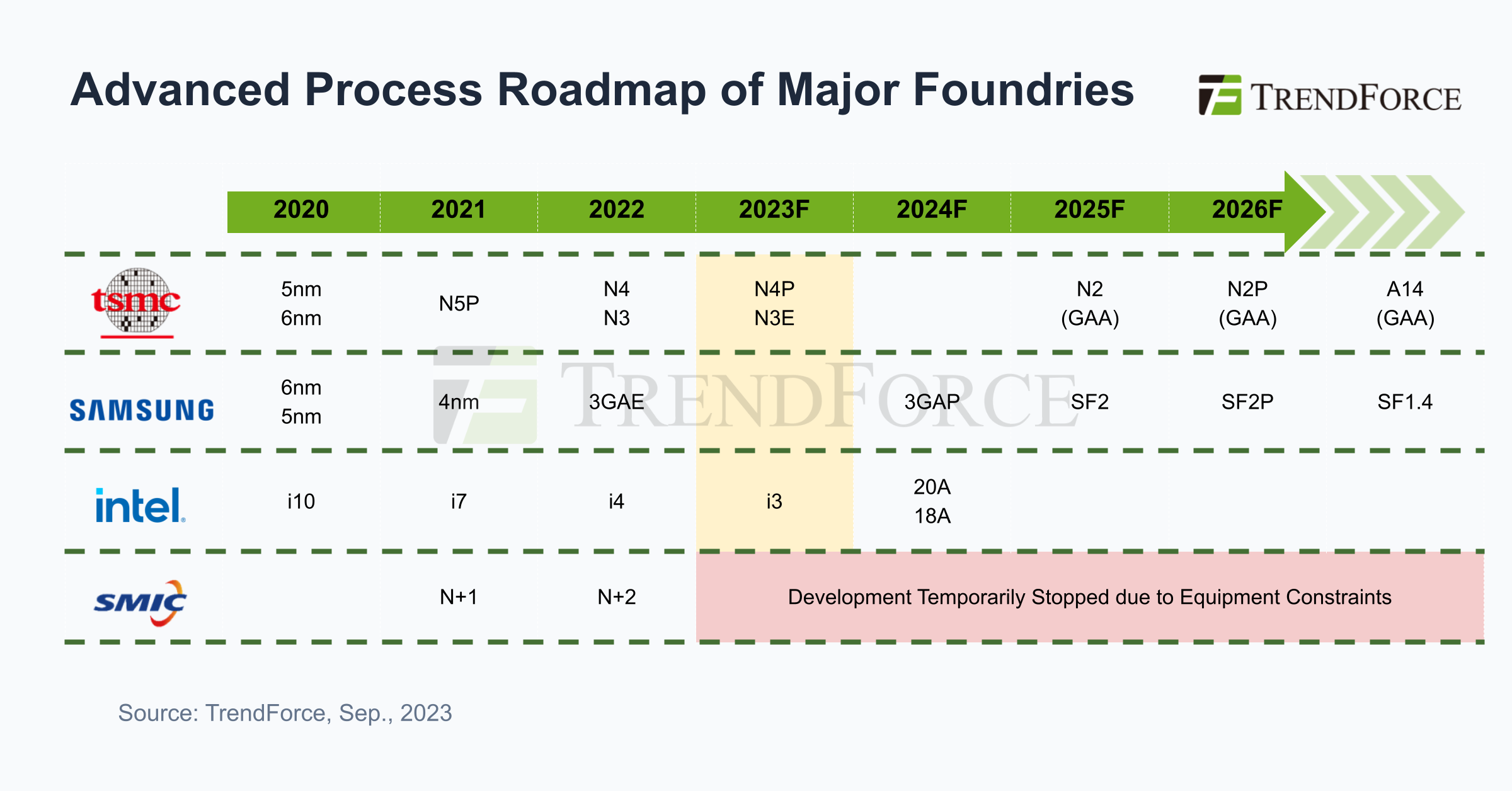

Currently, the most advanced production technology in the industry is the 3-nanometer process, manufactured by Samsung Electronics and TSMC. With Intel securing the first ASML lithography machine and updating its latest manufacturing roadmap, and with the increasing collaboration between Rapidus and IBM, the competition for the 2-nanometer advanced process has significantly expanded to include TSMC, Intel, Samsung and Rapidus.

According to Marvell’s press release, it has stated that Marvell has transitioned from a follower to a leader in integrating advanced node technology into silicon infrastructure.

Marvell first bringing advanced node technology to infrastructure silicon with its 5nm platform, followed by the release of several 5-nanometer designs and the profolio of the first silicon infrastructure product lineup based on TSMC’s 3-nanometer process.

“Tomorrow’s artificial intelligence workloads will require significant and substantial gains in performance, power, area, and transistor density. The 2nm platform will enable Marvell to deliver highly differentiated analog, mixed-signal, and foundational IP to build accelerated infrastructure capable of delivering on the promise of AI,” said Sandeep Bharathi, chief development officer at Marvell.

TSMC commenced mass production of its 3-nanometer process in 2022, with profitability realized starting from the third quarter of 2023. By the fourth quarter of 2023, the 3-nanometer process contributed to 15% of wafer revenue, and its revenue share has been steadily increasing.

According to TrendForce, the foundry market is expected to grow by 7% in 2024, largely attributed to TSMC’s ramp-up of its 3-nanometer process. This has further increased TSMC’s market share.

During the earnings call in the fourth quarter of 2023, TSMC announced that its 2-nanometer process (N2) would utilize Nanosheet transistor structures. It is anticipated that N2 will commence mass production in 2025, leading the industry in terms of density and energy efficiency.

The N2 backside power delivery solution is slated for release in the latter half of 2025 and is expected to enter mass production in 2026, primarily targeting the High-Performance Computing (HPC) sector.

Furthermore, due to the current high demand for 2-nanometer processes from all AI innovators worldwide surpassing that for 3-nanometer processes, almost all AI innovators are collaborating with TSMC on 2-nanometer process technology. The main applications are primarily focused on high-performance computing (HPC) and smartphones.

Consequently, TSMC has announced plans to expand its production capacity for 2-nanometer processes. Originally, two 2-nanometer fabs were planned for the Kaohsiung facility, but now consideration is being given to constructing a third 2-nanometer fab.

Samsung commenced mass production of its 3-nanometer process in June 2022. According to the latest industry reports, Samsung has developed a “second-generation 3-nanometer” process, renamed as “2-nanometer”, with plans for mass production before the end of this year.

At the 2023 Samsung Foundry Forum, Samsung Electronics unveiled the latest roadmap for its 2-nanometer process. Samsung Electronics President and Head of Foundry Business, Siyoung Choi, disclosed that Samsung will first mass-produce 2-nanometer chips for mobile terminals starting from 2025. Subsequently, in 2026, the technology will be applied to high-performance computing (HPC) products, followed by expansion to automotive chips by 2027.

Unlike TSMC, which opted for Gate-All-Around (GAA) structure at the outset of its 2-nanometer process, Samsung has been utilizing GAA structure since its 3-nanometer process. This suggests that Samsung may have more experience in new structures compared to TSMC, thus giving Samsung an advantage in its 2-nanometer node.

In the past, when Samsung Electronics transitioned from 7-nanometer to 5-nanometer process technology in 2020, the second generation 7-nanometer process technology was renamed as 5-nanometer process technology.

Samsung Electronics’ 7-nanometer process technology became the world’s first to use Extreme Ultraviolet (EUV) lithography in 2019, making it more stable and enabling the company to further shrink transistor sizes. This was also the reason for renaming the second generation 7-nanometer process to 5-nanometer process at that time.

A report from the Business Korea has indicated that Samsung Electronics recently secured an order from the Japanese AI startup Preferred Networks (PFN) to produce semiconductors based on the 2-nanometer process.

It is reported that PFN has been collaborating with TSMC since 2016, but this year, it has decided to produce the next generation of AI chips at Samsung’s 2-nanometer node. According to the agreement, Samsung will utilize its latest 2-nanometer chip fab technology to manufacture AI accelerators and other AI chips for PFN.

As per Intel’s previously announced plans, the company aims to catch up with and surpass TSMC by 2024 or 2025. At this year’s “Direct Connect” conference hosted by Intel Foundry Services, the company unveiled its latest technological roadmap.

Intel has reported that its primary product, Clearwater Forest, which is under the 18A process, has been completed and is set for production in 2025. Intel’s 18A process is often compared with TSMC’s N2 (2-nanometer) and N3P (3-nanometer) processes in terms of performance, with each company advocating for its own advantages.

Intel CEO Pat Gelsinger emphasizes that both 18A and N2 utilize GAA transistors (RibbonFET), but the 1.8-nanometer node will adopt BSPND, a backside power delivery technology that optimizes power and clock. TSMC, on the other hand, believes that its N3P (3-nanometer) technology will rival Intel’s 18A in power consumption, performance, and area (PPA), while its N2 (2-nanometer) will surpass it in all aspects.

Additionally, Intel’s 20A manufacturing technology is reportedly scheduled for launch in 2024, introducing two technologies: RibbonFET surround gate transistors and backside power delivery network (BSPDN). These aim to achieve higher performance, lower power consumption, and increased transistor density.

Meanwhile, Intel’s 18A production node aims to further refine the innovations of 20A and provide additional PPA improvements from late 2024 to early 2025. Per Intel’s statements regarding its fab processes, its 2-nanometer technology is expected to be the earliest to debut.

Of particular note, Intel announced for the first time at the conference the development of 14A (1.4nm) and its evolutionary version, 14A-E. Intel’s 14A process is the industry’s first node to utilize ASML High-NA EUV lithography tools, making Intel the first company in the industry to acquire cutting-edge High-NA tools. Intel expects to develop 14A by 2027.

In addition to the aforementioned semiconductor foundries, a Japanese company, Rapidus, is worth noting as well. Established in August 2022, Rapidus was jointly founded by eight Japanese companies including Toyota, Sony, NTT, NEC, SoftBank, Denso, NAND Flash giant Kioxia, and Mitsubishi UFJ.

On January 22nd of 2024, Rapidus President Junichi Koike announced during a press conference that construction of the Rapidus 2-nanometer chip fab in Japan is progressing smoothly, and the trial production line is scheduled to commence operations in April 2025 as planned. Additionally, there are plans for the construction of a second and third facility in the future.

In September of last year, Rapidus began construction of Japan’s first logic chip fab, “IIM-1,” in Chitose City, Hokkaido, capable of producing chips below 2 nanometers. It is reported that the fab is expected to be completed by December of this year.

Previously, Rapidus signed a collaboration agreement with IBM to develop technology based on IBM’s 2-nanometer process. IBM had already introduced the world’s first 2-nanometer process chip back in 2021. Similarly, IBM’s 2-nanometer process also utilizes GAA (Gate-All-Around) structure. This partnership provides Rapidus with the technical support necessary for advanced process development.

Read more

(Photo credit: TSMC)