Lý do để biết IGZO

Interest in monolithic 3D integration is driven by both compute-in-memory applications and a more general need for increased circuit density. Compute-in-memory architectures seek to reduce the power requirements of machine learning workloads, which are dominated by the movement of data between memory and logic components. Even in conventional architectures, though, placing high-density, high-bandwidth memory in close proximity to logic circuits can improve computation speed and reduce resistive losses.

However, integrating devices into the upper layers of conventional CMOS circuits imposes stringent limitations. To avoid copper diffusion, BEOL process temperatures are limited to 400°C or less. Indium-based oxide semiconductors are one of the few classes of materials that can meet this requirement while delivering acceptable circuit performance. Moreover, they are well-established in display applications, with more process maturity than germanium. [1] And as Seung Hyun Oh of KAIST said in work presented at this year’s VLSI Technology Symposium [2], they provide better mobility than amorphous silicon.

Among these materials, indium gallium zinc oxide (IGZO) in particular has a wide bandgap (3.0 eV or more, depending on composition), exceptionally low leakage, and high mobility. Unfortunately, the IGZO devices demonstrated so far struggle to deliver adequate on-state current.

Optimizing IGZO devices

On-state current improvement will require reduced interface scattering and better control of source and drain resistance. While early work on IGZO devices used sputtering deposition, ALD is more compatible with the dimensions that 3D integration will require. It is inherently conformal, and gives more composition flexibility. For instance, at last year’s VLSI Technology Symposium, Jie Zhang and colleagues at Purdue University discussed IGZO devices fabricated with supercycles of 1 ZnO cycle, 1 Ga2O3 cycle, and 10 In2O3 cycles. [3] Each supercycle deposited about 1.25 Å of material, with a total channel thickness of about 1.5nm.

With these devices, they achieved a very good subthreshold swing (SS) of 68mV/decade and an on/off current ratio in excess of 1011. This year, researchers at Samsung explored a variety of In:Ga:Zn ratios to improve threshold voltage and on-current. [4] Their best results, with on-current in excess of 22 μA/μm, came from the In-rich, Zn-poor part of the composition space.

Besides the composition of the semiconductor itself, hydrogen concentration in the bottom oxide was an important factor in overall device performance. Hydrogen migration into the channel led to broken metal-oxygen bonds, the Samsung Group said, creating O2 dimers. Reducing hydrogen in the bottom oxide reduced it in the channel, shifting the threshold voltage in a positive direction.

The interlayer between the IGZO material and the device contacts is another important factor. Oxidation of the contact metal should be avoided because it increases device resistance. Contact resistance is especially important because it becomes a larger share of the total as the channel dimension shrinks. Sumi Lee and colleagues at Purdue showed that, when making contact to pure indium oxide, the charge neutrality level is above the Fermi level. [5] Interface traps act as donors, contributing negative charge that accumulates at the interface. The result is a negative Schottky barrier and low contact resistance. Gallium and zinc doping shift the charge neutrality level down, below the Fermi level and into the IGZO band gap. Acceptor-like interface traps deplete charge, and the Schottky barrier height and contact resistance increase. Tuning the IGZO composition allows manufacturers to minimize the contact’s Schottky barrier height.

One of the major process challenges for oxide semiconductors is the need to control oxygen content. Oxygen vacancies in IGZO can contribute to unstable threshold voltage behavior. Unfortunately, oxygen plasma doping treatments cause surface damage. Post-deposition thermal annealing also has been used, but uniform annealing of very small features is challenging.

Instead, researchers at the National University of Singapore placed an indium tin oxide (ITO) cap layer on top of the IGZO channel, using tin to satisfy dangling oxygen bonds. [1] Seung Hyun Oh’s group used a fluorine-doped cap layer formed by so-called “initiated CVD.” [2] In initiated CVD, vaporized monomers and an initiator compound are injected into the process chamber. They dissociate and absorb on the surface, then polymerize to form a thin film with the intended dopant. Metal-fluoride bonds are stronger than metal-oxide bonds, so the fluorine dopant displaced weakly bonded oxygen atoms. In this work, threshold voltage (from -1.3 to 0.9 V), mobility (from 11.8 to 29.2 cm2/V-s), and sub-threshold swing (from 115 to 62 mV/decade) all improved. There were fewer dangling bonds at the IGZO/SiO2 interface, Oh said, and fewer electron traps.

Device structures for logic and memory

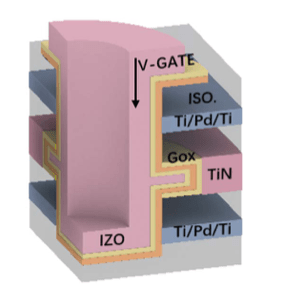

IGZO lends itself to a variety of device structures, depending on the intended application. Because its process temperature is so low, it is relatively easy to stack layers, either for stacked nanosheet devices or for vertical integration of complete transistors. As in silicon, stacked nanosheets offer one answer to the problem of low current in scaled devices. Researchers at Tsinghua University demonstrated devices with a C-shaped vertical channel surrounding a vertical gate and flanked by lateral gates. Fabrication used a 3D NAND-like integration scheme to pattern a stack of lateral gates in one step, followed by deposition of the channel and vertical gate. [6]

Fig. 1: Vertical dual-gate transistor. [6]

DRAM cells rely on a capacitor to store the cell value, with an accompanying transistor write, read, and refresh the value. S. W. Yoo and colleagues at Samsung implemented a 1T1C vertical IGZO DRAM cell. In devices like these, the source and drain are not fabricated at the same time and may not have symmetric dimensions. While standard electrical measurements give the combined source and drain resistance, optimizing asymmetric devices requires measuring the source and drain resistance separately. The Samsung Group achieved this by measuring the Id-Vg transfer curves under both Vd-high and Vs-high conditions. When a bias is applied to the transistor source, the Fermi level at the source contact rises, and the drain resistance is much larger than the source resistance. When a bias is applied at the drain contact, the opposite is true. By measuring both, the group was able to extract separate values for the source and drain resistance. [7]

Especially for machine learning applications, it’s desirable to store non-binary values corresponding to model weights. Researchers at imec demonstrated a 2T1C cell in which one transistor writes a value to the storage capacitor. That value serves as the gate voltage for a second read transistor. The product of the capacitor weight (wij) and the activation input to the read transistor (actij) accumulates in the output register. [8] With IGZO transistors, though, the extremely low leakage current allows further simplification — a capacitor-less 2T0C design, in which the gate capacitor of the read transistor serves as the storage element. [9]

Fig. 2: Schematic for 2T1C IGZO gain cell. Source: imec

Compute-in-memory modules that use capacitor-less memory cells to calculate multiply-accumulate operations for machine learning models may lie at the outer perimeter of foreseeable IGZO transistor applications. In the near term, though, low leakage, ease of integration, and improving device current may make them a welcome addition to low-power design toolboxes.

References:

- S. Hooda, et al., “Overcoming Negative nFET VTH by Defect-Compensated Low-Thermal Budget ITO-IGZO Hetero-Oxide Channel to Achieve Record Mobility and Enhancement-mode Operation,” 2023 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits), Kyoto, Japan, 2023, pp. 1-2, doi: 10.23919/VLSITechnologyandCir57934.2023.10185266.

- Seung Hyun Oh, et al., “Overcoming Performance Limitation of IGZO FET by iCVD Fluorine Doping,” 2024 IEEE Symposium on VLSI Technology and Circuits, Honolulu, Hawaii, 2024, paper T12-1.

- J. Zhang et al., “First Demonstration of BEOL-Compatible Atomic-Layer-Deposited InGaZnO TFTs with 1.5 nm Channel Thickness and 60 nm Channel Length Achieving ON/OFF Ratio Exceeding 1011, SS of 68 mV/dec, Normal-off Operation and High Positive Gate Bias Stability,” 2023 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits), Kyoto, Japan, 2023, pp. 1-2, doi: 10.23919/VLSITechnologyandCir57934.2023.10185312.

- Jee-Eun Yang, et al., “a-IGZO FETs with High Current and Remarkable Stability for Vertical Channel Transistor(VCT) / 3D DRAM Applications,” 2024 IEEE Symposium on VLSI Technology and Circuits, Honolulu, Hawaii, 2024, paper T4.5.

- Sumi Lee, et al., “Positive to Negative Schottky Barrier Transition in Metal/Oxide Semiconductor Contacts by Tuning Indium Concentration in IGZO,” 2024 IEEE Symposium on VLSI Technology and Circuits, Honolulu, Hawaii, 2024, paper T16-3.

- Ziyi Liu, et al., “A Dual-Gate Vertical Channel IGZO Transistor for BEOL Stackable 3D Parallel Integration for Memory and Computing Applications,” 2024 IEEE Symposium on VLSI Technology and Circuits, Honolulu, Hawaii, 2024, paper T12-4.

- S. W. Yoo, et al., “A Novel Method for Extracting Asymmetric Source and Drain Resistance in IGZO Vertical Channel Transistors,” 2024 IEEE Symposium on VLSI Technology and Circuits, Honolulu, Hawaii, 2024, paper T16-5.

- S. Subhechha et al., “Demonstration of multilevel multiply accumulate operations for AiMC using engineered a-IGZO transistors-based 2T1C gain cell arrays,”, IMW 2023.

- A. Belmonte et al., “Tailoring IGZO-TFT architecture for capacitorless DRAM, demonstrating > 103s retention, >1011 cycles endurance and Lg scalability down to 14nm,” 2021 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2021, pp. 10.6.1-10.6.4, doi: 10.1109/IEDM19574.2021.9720596.