Hợp lý hóa thiết kế SoC với các giải pháp tích hợp và IP nâng cao

As system-on-chip (SoC) complexity grows, so does the necessity for products that seamlessly connect IP and streamline integration processes, minimize manual errors, and enhance productivity. The emphasis on physical awareness across solutions significantly reduces the iterative cycles of NoC placement and routing. By ensuring low latency and high efficiency, these advanced integration solutions meet stringent performance and power requirements, facilitating rapid development cycles and enabling SoC design teams to deliver cutting-edge applications quickly and reliably.

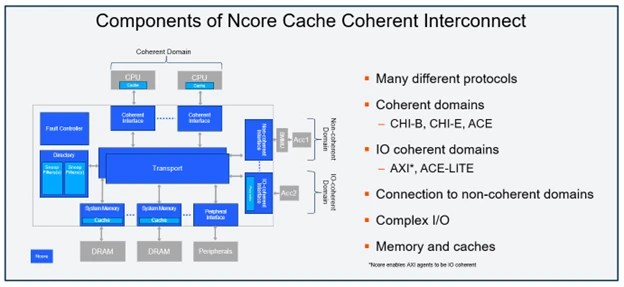

Arteris, a provider of system IP that accelerates SoC creation and integration, addresses the growing complexity of SoC designs with advanced products, including NoC IP and SoC integration automation software. Our NoC IP products support multiple processor IPs, such as Armv9 Cortex and RISC-V application processors from numerous vendors. Ensuring such compatibility is crucial for achieving high performance in complex SoCs. Arteris multi-protocol support allows seamless integration of IPs connected to the same NoC fabric, offering flexibility with fully coherent agent interfaces such as CHI-E, CHI-B, and ACE, IO-coherent interfaces such as ACE-Lite, and AXI for non-coherent sub-systems.

Ncore, FlexNoC, CodaCache, and Magillem Registers provide a comprehensive solution for modern SoC design, ensuring efficient integration of hardware components. Ncore’s cache coherent NoC IP supports low-latency integration of hardware accelerators. FlexNoC’s physical awareness capabilities enhance performance, lowering power consumption and decreasing die size. At the same time, CodaCache operates as a last-level cache (LLC) controller for FlexNoC, drastically increasing system performance compared to directly connected DRAM.

Magillem Registers automates the generation of the hardware/software interface (HSI), maintaining consistency across various components. These products streamline the SoC design process, enabling rapid development cycles and robust architecture.

Ncore enables low-latency and high-bandwidth connectivity

Ncore cache coherent NoC IP ensures low latency integration of hardware accelerators into a coherent domain, delivering the speed and efficiency required for cutting-edge applications in complex SoCs. Utilizing this interconnect can save design teams more than 50 years of engineering effort per project compared to manually generated interconnect solutions.

Fig. 1: Tackle complexity with Ncore, cache coherent interconnect IP from Arteris.

Ncore’s configurability and scalability allow SoC designers to meet specific power, performance and area (PPA) requirements with flexible fine-tuning of the NoC architecture. Additionally, the cache coherent NoC supports direct connections for heterogeneous and asymmetric systems and other flexible connectivity options, making it adaptable to various applications across automotive, industrial, communications and enterprise computing markets. Furthermore, Ncore is ISO 26262 certified for ASIL B and ASIL D, meeting stringent safety requirements for automotive and industrial applications.

FlexNoC 5 physically aware interconnect for optimized SoC design

FlexNoC 5, Arteris’ latest non-coherent NoC interconnect IP, has physical awareness that eliminates the need for lengthy placement and route iterations, significantly reducing development time. This technology enables 5X faster physical convergence over manual refinements, leading to improved performance, lower power consumption, and reduced die size.

FlexNoC instances can also be imported into the Arteris Magillem Connectivity flow to interface with other third-party IP blocks for easier SoC integration.

Fig. 2: Modern SoCs require multiple interconnects for optimal performance – Ncore cache coherent and FlexNoC non-coherent interconnects work together.

FlexNoC 5 supports multi-clock, power, and voltage domains with unit-level clock gating and several topologies, Arm AMBA 5 protocols, and IEEE 1685 IP-XACT. The interconnect also includes general optimizations for lower areas, achieving up to a 30% reduction for some NoC elements depending on the configuration. Additionally, a Functional Safety (FuSa) option complies with ISO 26262 standards up to ASIL D, increasing its suitability for safety-critical applications.

Magillem Registers automates the hardware/software interface

Arteris continuously enhances its Magillem Registers (incorporating CSRCompiler technology), and Magillem Connectivity SoC Integration Automation tooling, reducing manual errors and improving productivity. CSRCompiler technology inside of Magillem Registers supports rapid, iterative designs. It ensures consistency across multiple teams, automating the generation of HSI requirements from high-quality RTL and software to design verification and documentation. Utilizing SystemRDL 2.0, this software solution ensures consistency across various views and organizations without time-consuming manual scripting and editing.

Fig. 3: Unified specification and compilation flow.

Magillem Registers HSI database offers centralized and customized HSI information. It compiles thousands of registers within seconds and millions within minutes. The software’s adaptable architecture supports various input formats into a single source, ensuring efficient production of all required formats and helping avoid errors in address map deployment. This comprehensive approach reduces the HSI development process by up to one-third.

Conclusion

Arteris’ capabilities include keeping pace with the evolving SoC landscape and setting new benchmarks in efficiency, reliability, and performance. Arteris solutions address the intricate challenges of modern SoC design by focusing on physical awareness and advanced automation. These innovations enable engineers to push the boundaries of what is possible, crafting high-performance applications that drive the future of technology.

For additional information:

Videos:

White Paper:

For more in-depth insights and to explore our comprehensive range of solutions, visit Arteris.

Andy Nightingale

Andy Nightingale is vice president of product management and marketing at Arteris. He has more than 36 years of experience in the high-tech industry, including 23 years in various engineering and product management positions at Arm.