Hệ sinh thái bán dẫn đang ứng phó với những thách thức toàn cầu của nó như thế nào

The semiconductor industry is changing rapidly, with government support for re-shoring capacity creating new interplay among resources in Asia, the U.S., and Europe—even as the industry develops and sustains new technologies like HBM and heterogeneous integration. Geopolitical factors such as the CHIPS (Creating Helpful Incentives to Produce Semiconductors for America) Act, the scarcity of skilled engineers, and new AI-related performance demands are all contributing to industry challenges and rapid evolution.

What does this mean for semiconductor test? Automated test equipment (ATE) companies are playing a crucial role in addressing these challenges by adapting their technologies, enhancing automation, and collaborating closely with semiconductor manufacturers. Test resources are proving essential, ensuring the industry can continue to innovate and meet the growing demands of a global market.

Geopolitics and semiconductor impact

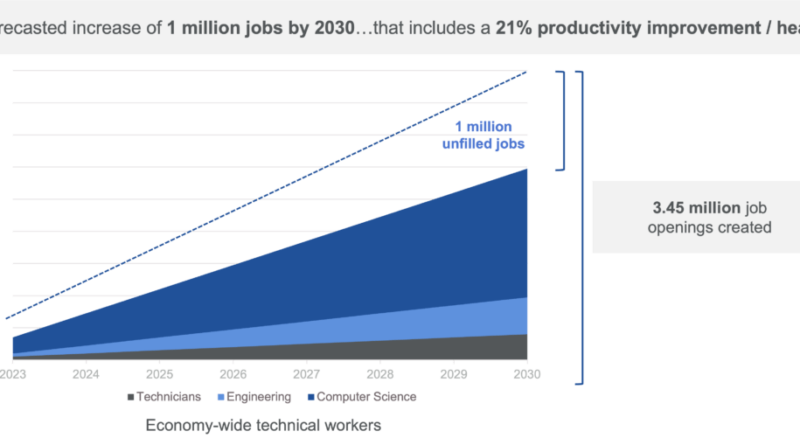

The semiconductor marketplace is shifting, with government support for manufacturing capacity being re-shored to the U.S. and Europe. The CHIPS Act, in the US, is a significant legislative initiative to bolster domestic semiconductor manufacturing and research. Its substantial funding and incentives are intended to address vulnerabilities exposed by supply chain disruptions and geopolitical tensions. Funding also supports workforce development, with the U.S. facing an industry talent shortage estimated at 70,000 to 90,000 workers over the next few years, and worldwide upwards of a million unfilled jobs by 2030, even with productivity gains.

The CHIPS Act also funds advanced research in semiconductor technologies—fostering a need for innovation in semiconductor testing methodologies and cutting-edge test equipment. This is crucial as the test sector evolves to handle the complexities of chips featuring advanced packaging and heterogeneous integration, helping ensure the industry is well-positioned to handle the broad demand for AI and high-performance processing.

Similar initiatives are underway in Europe and Asia, each striving to enhance its infrastructure. Interplay between regions is complex: Asia, particularly Taiwan and South Korea, remains a powerhouse in semiconductor manufacturing, even as the U.S. and Europe are investing heavily in their own semiconductor ecosystems.

The CHIPS Act’s impact on the test sector is profound. The influx of capital is increasing capacity for semiconductor production, which in turn requires more test equipment and services. Domestic semiconductor test resources are in greater demand as new fabs and assembly houses are established in the U.S.

New demands and new opportunities for test

These government-backed investments in infrastructure come at a critical juncture in semiconductor design, development, and test. The drive toward AI has increased focus on the performance and reliability of advanced digital chips—global demand is high for applications that require super-fast performance but come with increased complexity and power needs.

As semiconductor nodes shrink (for example below 5nm geometries), the complexity of ensuring their performance, reliability, and power efficiency increases exponentially. Each step forward in miniaturization introduces new challenges in manufacturing precision, thermal management, and defect detection. Technology progress increases overall pressure on all fab tools, including the ATE systems on which manufacturers rely for final device yields that ultimately translate to revenue.

It is well known now that the era of gains achieved by shrinking semiconductor process nodes is slowing down, necessitating innovations in design, materials, and packaging to maintain the trajectory of Moore’s Law. Chipmakers are adopting advanced packaging technologies to meet the required processing speeds, including multiple heterogeneous integrated semiconductor dies (chiplets) and 2.5D/3D packaging structures. This heightens the pressure on fabs to reliably produce Known Good Die (KGD) and Known Good Interposers (KGI), resulting in increasingly sophisticated testing methodologies required to verify the performance and reliability of individual dies before they are assembled into a larger system.

ATE sector responds to the increasing complexity of converging factors

Teradyne is committed to staying ahead of these demands, ensuring that the global semiconductor ecosystem continues to innovate and thrive in the face of unprecedented challenges.

To meet the needs of these dramatic changes in the global semiconductor arena, the company has incorporated a flexible test strategy. This includes the ability to shift testing across the manufacturing flow to effectively manage the cost of quality. Early testing minimizes scrap costs, while late-stage testing ensures thorough quality control. It’s a balanced approach that maintains quality throughout testing operations, capitalizing on data analytics, reducing costs, and improving yields.

More on shift left and shift right

2.5D/3D packaging indeed advances Moore’s Law, but its economic viability depends on reducing defect escape rates (the number of defects that make it all the way to production) early in manufacturing to cut scrap costs. Shifting tests left or right in the process helps achieve this and minimize overall costs.

Increasing test coverage early is known as shift left, occurring during wafer inspection and partial packaging to maximize KGD which helps reduce future packaging costs. However, this can raise test costs and must be weighed against the benefits of reduced scrap.

Shift right strategies increase test coverage later in the process to detect defects and maintain quality. This approach leverages higher parallelism in final (or system level) tests to reduce costs while meeting quality goals. High-yield tests can be moved to these later stages to optimize efficiency.

The goal is to balance quality and yield throughout manufacturing, optimizing overall cost. Strategies include reducing scrap costs by lowering defect escape rates in wafer probing, as well as efficiently conducting mass production testing to lower test costs. Ultimately, the decision to shift left or right is supported by analytics in a dynamic and continuous process. With valuable data at hand, test strategies can be adjusted throughout the chip manufacturing process, creating a closed-loop of improvement to increase yield rates while minimizing test costs.

Flexible test strategies meet the challenge

Today’s dynamic test coverage also combines ATE, like Teradyne’s UltraFLEXplus, with system level test (SLT), which can be done on Teradyne’s Titan platform. SLT emulates real-world conditions for optimal validation of integrated semiconductor devices and is particularly useful for advanced technologies like System-on-Chip (SoC) and System-in-Package (SiP), effectively identifying faults, keeping costs in check, and improving yields through data analytics.

Pre-integration testing ensures that only functional die and interposers are used in final packages, reducing defects via highly effective KGD and KGI processes. For 3D stacked ICs, comprehensive reliability and performance testing are handled via sophisticated 3D-DFT test access architecture.

Crucially, ATE’s data analytics help manufacturers achieve greater control in the fabrication process by offering insights into trends and anomalies. AI further aids in analyzing these trends—optimizing test parameters and making real-time, proactive adjustments for yield improvement and cost reduction possible. Teradyne’s Archimedes analytics solution delivers an open development environment that enables real-time analytics, on the edge, with the flexibility to deliver both out of the box and custom solutions that are easy to deploy.

Similarly, silicon photonics, which is designed to reduce data center power consumption, necessitates the development of simultaneous digital and photonics testing. As photonics are more routinely integrated with electronics for high data transfer rates and low power consumption, test solutions must be optimized for co-packaged optics.

Tapping into data and automation for next-gen ATE

As we look ahead over the next few years, we can anticipate greater demand for specialized test equipment for new semiconductor materials, such as SiC and gallium nitride (GaN), as well as integrated photonics. This includes increased capabilities for high voltage/high current and low voltage/low current testing, effectively handling different materials within a single package.

End-to-end automation is likely to play a crucial role, reducing human intervention and minimizing errors with fully automated testing processes from wafer to final package. ATE will continue to leverage AI and machine learning to enhance testing accuracy, predict component failures, and optimize test parameters in real time.

AI-driven data analytics will help identify patterns and trends, leading to proactive quality control and yield improvement. Teradyne is supporting the industry’s moves to add AI through the SEMI Smart Data-AI Initiative, a platform that drives value creation from data and AI, specific to the semiconductor ecosystem. As a member of the initiative, Teradyne is working toward standardizing test data outputs, which encourages collaboration without fear of IP exposure or vendor lock-in.

It’s clear the intersection of AI, advanced semiconductor technology, and geopolitical dynamics is shaping the future of our industry. Through flexible, collaborative, and innovative test strategies, Teradyne is committed to ensuring the reliability and excellence of semiconductors, paving the way for a future where AI can reach its full potential.