ECO dễ dàng logic và chức năng tại #61DAC

I first visited Easy-Logic at DAC in 2023, so it was time to meet them again at #61DAC in San Francisco to find out what’s new this year. Steven Chen, VP Sales for North America and Asia met with me in their booth for an update briefing. Steven has been with Easy-Logic for six years now and earned an MBA from Baruch College in New York. This was the fifth year that they exhibited at DAC.

A functional Engineering Change Order (ECO) is a way to modify the gate-level netlist, post-synthesis with the least amount of disruption and effort to minimize costs. Fixing a logic bug post-silicon can often be remedied with a Post-Layout ECO, where spare cells can be connected with updated metal layers, keeping mask costs low for a new silicon spin.

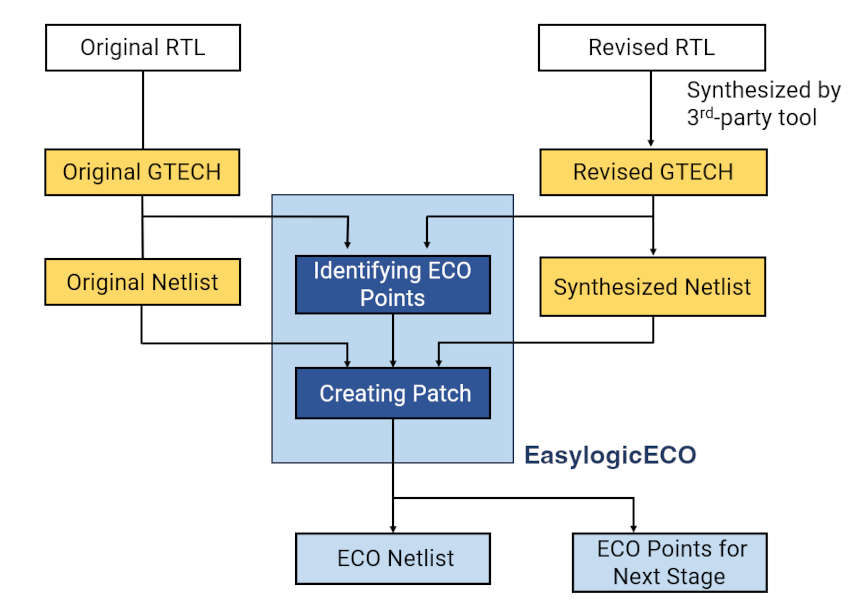

Their booth display showed an EDA flow and where their four ECO tools fit into the flow.

Something new in 2024 is the GTECH design flow from Easy-Logic, it’s a way to simplify the functional ECO flow for ASIC designs. With GTECH the user can quickly identify the ECO points, the gate-level circuits to be modified, over the traditional RTL-to-RTL design flow. With the EasylogicECO tool you continue to employ the smallest ECO patch size by refining the ECO point, reducing design complexity and speeding the time required. Using the GTECH design approach fits into your existing EDA tool flows, making it quick to learn and use. There was a press release about GTECH in May 2024 and at DAC they were showing demonstrations of this capability.

Steven talked about how even a junior engineer can use this tool easily, and that when silicon comes back from the fab and isn’t working 100% that a full re-spin can require 100 mask changes, while a metal ECO can use only 30-40 mask changes, so a much lower cost to implement. In the old days engineers used to do manual ECO changes, but that approach required too much engineering effort and was error prone. With an automated approach it dramatically improves the chance of success. In most cases where a designer may give up on a manual metal ECO if the spare cells needed are expected to exceed 50 because the signal was flatten and is too hard to trace. With the capability of producing a smaller patch with quicker runtime, EasylogicECO can help designers increase their success rates on metal ECO projects. This approach is widely adopted by most IC design houses in Asia, focusing on cost reduction by having fewer metal layers change and produces the quickest product launch. EasylogicECO is playing an important role driving this metal ECO approach.

The EasylogicECO tool works in process nodes that are planar CMOS, FinFET, even with leading processes like 3nm. Semiconductor Review APAC magazine recognized Easy-Logic as one of the top 10 EDA vendors in July 2023.

Summary

Easy-Logic was founded in 2013, based in Hong Kong and had their first order by 2018 for ECO tools. By 2021 they expanded into an R&D center in Shenzhen, adding new ECO products. Today they have four ECO tools and over 40 happy customers from around the globe. Adding the GTECH design flow this year makes it even easier to use their ECO tool, so their momentum continues to grow in the marketplace. I look forward to watching their technology and influence expand.

Related Blogs

Share this post via: