Điều hướng sự phức tạp gia tăng trong bao bì tiên tiến

As chips evolve toward stacked, heterogeneous assemblies and adopt more complex materials, engineers are grappling with new and often less predictable sources of variation. This is redefining what it means to achieve precision, forcing companies to rethink everything from process control and in-line metrology to materials selection and multi-level testing.

These assemblies are the result of increasing demands for performance, integration, and miniaturization, which are not possible using a reticle-sized chip and two-dimensional scaling. Instead of a single, planar system-on-chip, advanced packages may incorporate multiple die of varying functions, from RF and analog to heterogeneous logic and memory, each with its own thermal, electrical, and mechanical requirements. Fine-pitch interconnects, through-silicon vias (TSVs), ultra-thin RDL layers, and intricate EMI shielding structures add further complexity. Even small deviations in assembly steps or material properties can ripple through the entire package, affecting yield, performance, and long-term reliability.

In this environment, the long-standing practice of relying on static process windows or manual operator intervention is no longer sufficient. Manufacturers are turning to advanced metrology, AI-driven process control, and feedback loops that integrate early prototyping with final test data to ensure the necessary precision to achieve yield targets in high-volume manufacturing (HVM). Nevertheless, what works for one advanced package may fail for another. Precision, which once was considered a matter of carefully tuning individual steps, now depends on a holistic system-level approach to managing variability.

“In older fabs, you might rely on fixed control limits or simple statistical process control (SPC) to detect when a process goes out of spec,” said David Park, vice president of marketing at Tignis. “But in advanced packaging, even subtle changes — like a slight temperature gradient in the chamber, a bit of contamination, or minor variations in gas flow — can push critical dimensions out of specification. Without advanced analytics or AI-driven tools to catch and correct these issues early, a process that once seemed stable suddenly can yield inconsistent results.”

Managing increased variation

Achieving the precision necessary for high yields in advanced packaging is not a matter of controlling a single variable, or even a few. Instead, it demands a holistic understanding of how every component and process step interacts, along with a readiness to adapt as unexpected results from these variabilities arise. Variability now manifests not just in lithographic dimensions or etch depths, but also in the way materials interact under thermal, mechanical, and electrical stress. As a result, even carefully planned designs fail to perform as intended once assembled.

“Chip manufacturers have to systematically reduce process variability to avoid wider control limits that impact quality and end of line yield,” said Russell Dover, general manager of the Service Product Line at Lam Research. “This is why SPC has been a fundamental methodology for the semiconductor industry almost from its very foundation. But for SPC to be effective, you need tight control limits.”

These variations often stem from the interplay of advanced substrates, low-k dielectrics, and process steps to form through-silicon vias (TSVs) and complex redistribution layers (RDLs). As more exotic materials and tightly packed structures enter the mix, ensuring uniform performance across all operating conditions becomes increasingly difficult.

“Meeting tight tolerances in new packaging designs requires accurate analysis of mechanical and electrical stack-ups,” said Mike Kelly, vice president of chiplets and FCBGA integration at Amkor. “As levels of process capability need to be increasingly higher, early identification of critical interactions guides investments in advanced process control to maintain process capability. This is essential to ensuring that even subtle sources of variability don’t undermine overall yield and reliability.”

Precision in bonding and warpage control

Achieving precision in bonding and warpage control has become increasingly challenging in advanced packaging as structures grow more complex and interconnect densities increase. Maintaining alignment during bonding processes, especially with ultra-thin substrates and high-density interconnects, requires exceptional precision to ensure mechanical and electrical reliability. Variations in material properties, coupled with thermal stresses during processing, can lead to bonding misalignment, void formation, and even complete interconnect failure.

“While copper pillar solder interconnect methods are becoming well-established, the challenge lies in achieving higher densities,” said Dick Otte, CEO of Promex Industries. “As we move from 100-micron pitch to 50-micron and even potentially 25-micron, maintaining co-planarity between the die and substrate becomes critical. With hundreds, or even thousands, of contacts, achieving a flatness within a few microns during the assembly cycle is essential for high yields.”

A critical factor in managing bonding precision is controlling substrate flatness and die placement accuracy. Substrates that fail to meet flatness specifications can cause uneven bonding and misaligned interconnects. Likewise, precise die placement is essential for ensuring that all electrical contacts function correctly. Advanced metrology methods such as optical profilometry and X-ray fluorescence are increasingly necessary to validate substrate quality, monitor metal plating uniformity, and assess interconnect integrity before bonding begins.

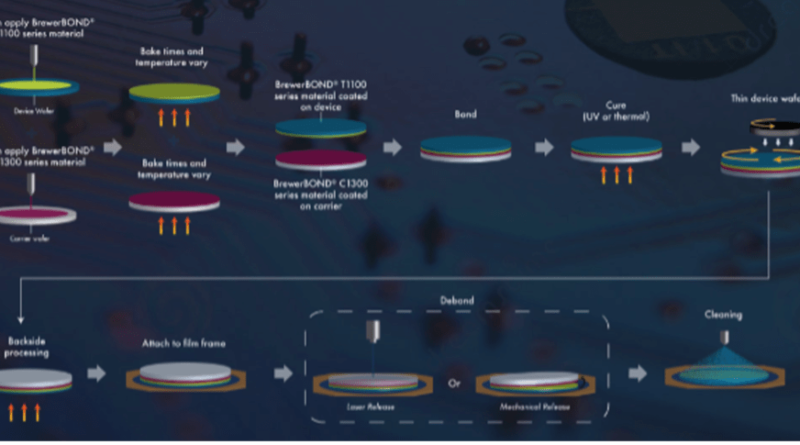

“When using temporary bonding materials as adhesives for populating carrier wafers with dies, it is critical that the placement of those dies be precise, and the shift of those dies to be essentially zero throughout the remaining process steps,” said Andrea Chacko, director of packaging solutions at Brewer Science. “It is critical that the dies are not only bonded with precise alignment on the carrier, but that the alignment is maintained through the die activation, dielectric bonding, Cu annealing, carrier release, and cleaning steps.”

Fig. 1: Typical process flow for device thinning to prepare dies for HBM stacking. Source: Brewer Science

Ensuring this precise alignment through all processing stages, from initial die placement to final cleaning, is paramount. Any shift or misalignment during these steps can compromise the integrity of the interconnects and negatively impact device performance. Therefore, the choice of temporary bonding materials, the optimization of process parameters such as bonding pressure and temperature, and the implementation of robust cleaning protocols are all critical to achieving high-yield and reliable bonding in advanced packages. These factors work in concert to minimize stress on the dies and maintain the desired level of planarity for successful interconnect formation.

“If the boards are not flat, a high-yield process is often impossible to achieve,” said David Fromm, COO at Promex. “We use optical profilometry to measure local and global substrate flatness and X-ray fluorescence to ensure proper plating thickness and composition. Performing proper measurements early on and linking them to device testing helps identify parameters critical to maintaining design intent.”

Bonding operations also must account for warpage control during thermal cycling, particularly in processes like flip-chip bonding and wafer-level packaging. As packages are exposed to high temperatures, differing coefficients of thermal expansion (CTEs) between layers can induce bending or warping.

“Achieving the required flatness for high-density interconnects is a significant challenge,” added Otte. “Trying to maintain flatness throughout the assembly cycle, including heating and cooling, requires controlling dimensions to within 1 part in 100,000. To put that in perspective, that’s like the width of a blade of grass compared to the length of a football field. With organic CTEs ranging from 30 to 50 ppm, even small asymmetry can lead to significant warpage.”

Implementing inline inspection and adaptive process control systems, supported by machine learning algorithms, can provide real-time adjustments to bonding parameters, helping to mitigate thermal-induced warpage. SPC further enhances production consistency, enabling tighter tolerances and reducing defects in bonded assemblies.

“In advanced semiconductor packages such as RF-SOI and 3D IC, testing must rigorously verify isolation, especially as frequency and power levels vary,” said Jeff Cheng, director of testing & packaging support at UMC. “For 3D-ICs in particular, testing for interconnect integrity, including checks for voids and delamination in TSVs, is crucial for device reliability.”

Thermal challenges to precision

As package architectures become more vertical and heterogeneous, thermal management emerges as a critical factor in sustaining precision. Stacked assemblies often place different die — each with its own power density and unique thermal behavior — into close proximity. In these multi-die configurations, temperature gradients can form as heat travels through layers of metals, dielectrics, and polymers, each with different CTEs. Uncontrolled, these variations induce mechanical stresses, cause warpage, and shift critical alignments, ultimately degrading yield and device reliability.

Thermal issues intertwine with other design variables, such as interconnect density and die placement, making early analysis essential. Engineers must consider how power delivery, interconnect routing, and cooling strategies interact to minimize hotspots and keep maximum die temperatures within safe limits. This holistic perspective enables them to preempt thermal-induced mechanical stresses and avoid misalignment issues before ramping into production.

“The density of the connections can have a big impact on the thermal aspects of the system,” said Keith Lanier, product management director at Synopsys. “Determining early on how many connections are required and how to arrange them to minimize thermal hotspots and maintain acceptable die temperatures is really critical.”

Thermal impact becomes even more pronounced as packages expand into fan-out configurations or adopt advanced panel-level packaging approaches. These techniques may involve coarser designs, RF elements, and diverse materials stacked in complex ways. Predicting and managing thermal behavior in these scenarios is more challenging than conventional wafer-level packaging, requiring careful simulation, material selection, and iterative refinement.

“Thermal becomes very challenging, especially if you stack these devices up,” said Shawn Nikoukary, senior director on the solution services team at Synopsys. “Even the best of the best are challenged with thermal issues. For fan-out panel-level packaging, which often involves coarser designs, the thermal challenges are going to be more pronounced compared to regular wafer-level packaging.”

Beyond the design stage, continuous measurement and iterative improvements help maintain thermal-related precision during manufacturing. Inline metrology and adaptive process control allow for real-time adjustments, such as modifying reflow profiles or tweaking bonding pressures, based on current thermal conditions. By correlating early assembly measurements with final test data, engineers can identify parameters most critical to preserving design intent amid thermal stress.

Increasing material complexity

The adoption of exotic materials in semiconductor packaging has become both an enabler and a challenge in precision manufacturing. As devices scale toward sub-5nm nodes and 3D architectures, material properties such as dielectric constant, thermal conductivity, and mechanical stability must be tightly controlled. High-k dielectrics, ultra-low-k insulators, and advanced underfill resins are now essential components, but their behavior can be unpredictable, especially under high-temperature and high-pressure processing conditions. Even slight deviations in material purity, molecular structure, or chemical reactivity can create significant variations in device performance, impacting both electrical characteristics and mechanical reliability.

“As we move toward more advanced materials, the need for increased control points and consistent communication between equipment is essential to avoid any process breakdowns,” said Matt Rich, controls engineering manager at Brewer Science. “The challenges we face with automation are evolving as the materials and processes become more complex. We’re now managing systems with far more control points, and any small deviation can impact the entire process.”

One of the most pressing challenges in using advanced materials is achieving deposition uniformity. Atomic layer deposition (ALD) and chemical vapor deposition (CVD) processes must produce ultra-thin, defect-free films over increasingly large wafers. In high-volume manufacturing, maintaining consistent film thickness within a tolerance of just a few angstroms is critical. Non-uniformities can cause dielectric breakdown, parasitic capacitance, and short circuits.

Likewise, barrier materials such as tantalum nitride or ruthenium used in interconnects must balance conductivity with electromigration resistance, a task further complicated by shrinking feature sizes and the need for conformal deposition within high-aspect-ratio structures. Achieving this delicate balance requires precise control over process parameters such as temperature, pressure, gas flow rates, and plasma conditions.

Advanced process control techniques, including in-situ monitoring and real-time feedback loops, are essential for ensuring consistent film quality and minimizing variability across the wafer. Furthermore, as wafer sizes increase, maintaining uniformity across the entire surface becomes even more challenging, requiring innovative reactor designs and optimized gas distribution systems. The development and implementation of advanced metrology techniques, such as spectroscopic ellipsometry and X-ray reflectivity, play a crucial role in characterizing film properties and providing the necessary feedback for process optimization.

Complex deposition chemistries

Additionally, the integration of heterogeneous materials in advanced packages magnifies chemical compatibility concerns. Materials used for plating, underfill, and encapsulation offer desirable properties but have mismatched thermal expansion coefficients. This mismatch leads to stress accumulation during thermal cycling, causing delamination, cracking, and void formation. Engineers must continuously refine chemical formulations, optimize layer thicknesses, and manage interface adhesion properties to counter these effects. Moreover, as process nodes shrink, the molecular dynamics at the material interface play an even more critical role, requiring deeper collaboration between material scientists and process engineers to ensure long-term device stability.

“For applications or downstream processes that require thermal stability up to 400°C without degradation or loss of mechanical stability, selection of the appropriate bonding material is critical,” said Brewer’s Chacko. “Materials such as thermoplastics, thermosets, UV-curable adhesives, and laser-release adhesives are used, depending on the thermal and mechanical demands of the application.”

Integrating design and process

As complexity intensifies, the boundary between package design and manufacturing execution continues to blur. Advanced packaging no longer allows a simple handoff from front-end design teams to back-end assembly engineers. Instead, achieving precision demands tight integration of design, materials engineering, and process control from the very start. This integration hinges on a deep understanding of the interplay between design choices and their impact on manufacturing processes.

Engineers increasingly must consider thermal profiles, mechanical stresses, and electrical coupling effects at the earliest stages of die partitioning and floor-planning. This co-design approach attempts to simulate chiplet placement, anticipate warpage, and map out material behavior under real operating conditions well before volume production begins. This shift toward a more holistic approach requires sophisticated simulation tools capable of handling the multi-physics nature of advanced packages. For example, finite element analysis (FEA) is crucial for predicting mechanical stress and warpage, while computational fluid dynamics (CFD) is essential for thermal analysis. Electromagnetic simulation tools are also necessary to model signal integrity and power delivery.

By aligning design decisions with known process capabilities and predicted material responses, engineers can guide process engineers toward choosing the right materials, deposition steps, or bonding parameters. This reduces the likelihood of unexpected variability downstream and ensures that all parties are working toward the same precision goals. This collaborative approach necessitates the development of common data formats and communication protocols that allow seamless information exchange between design and manufacturing teams.

Linking measurements, prototyping, and production

In advanced packaging, achieving precision is not solely about controlling parameters at high volume. It’s also about leveraging early-stage measurements to guide final outcomes. A robust feedback loop from prototyping to production enables engineers to detect where variability originates and address it before ramping to mass manufacturing. This loop is fueled by advanced metrology tools capable of capturing critical data at various stages of the packaging process.

“The layered nature of 3D-ICs necessitates electrical testing at multiple levels of integration, from individual layers before bonding to the complete assembly,” said UMC’s Cheng. “This multi-level testing, coupled with considerations for signal integrity, thermal management, and high-frequency signal handling, requires sophisticated test strategies and equipment, including consideration of design-for-test (DFT) methodologies such as IEEE 1838.”

A feedback-driven approach ensures that lessons learned from experimental runs or pilot lines influence the main production flow. Engineers can refine their process recipes, adjust bonding conditions, or re-select materials before committing to large-scale production. For instance, if early prototypes exhibit excessive warpage after thermal cycling, engineers can adjust the underfill material properties or modify the bonding process parameters to mitigate the issue. This iterative process is greatly enhanced by the use of machine learning algorithms, which can analyze large datasets of metrology data to identify correlations between process parameters and final device performance.

“In early-stage development builds, performing proper measurements during assembly and linking them to later device testing enables proper identification of parameters critical to maintaining design intent,” said Promex’s Fromm. “When scaling for higher volumes, continuous improvement is predicated on subsequent build-and-measure cycles, where build variability is increasingly understood and improvements made.”

Over time, these iterative refinements tighten process windows, reduce variability, and help meet yield targets in a high-mix, high-volume environment. This is particularly important in heterogeneous integration, where different dies with varying material properties and manufacturing processes are combined within a single package. The ability to quickly identify and address potential compatibility issues is crucial for achieving high yields and reliable performance.

“Successfully scaling hybrid bonding into high-volume manufacturing requires addressing challenges related to defect control, alignment precision, thermal management, wafer warpage, material compatibility, and process throughput,” added Chacko. “Solutions such as advanced inspection tools, metrology for defect reduction, high-precision alignment, and the careful selection of adhesive materials are critical to achieving reliable, high-yield results.”

Ensuring sustainable yields and profitability

With entire product lines depending on the yield and reliability of advanced packages, precision is no longer a nice-to-have. Variability — whether from warpage, deposition non-uniformity, or material incompatibilities — translates directly into economic losses. Each defective part incurs costs in material, labor, and opportunity. In today’s market, the ability to deliver high-performance, reliable packages on time and within budget is a critical competitive differentiator.

As the industry moves into applications that demand absolute reliability, such as high-performance computing, automotive radar, or network infrastructure, the cost of variability escalates. In these contexts, investing in precision-enhancing measures pays off by preventing rework, reducing scrap, and ensuring timely product launches that meet market expectations. This means that companies must prioritize investments in advanced metrology, process control, and simulation tools to minimize variability and maximize yield.

“We understand the value in making good measurements throughout the development of an assembly process,” said Fromm. “Without consistent control over these processes, achieving acceptable yields in advanced packages becomes extremely challenging. Yield hits from imprecision aren’t just about wasted material; they undermine your competitiveness and your ability to meet customer demands reliably.”

Digital twins and virtual fabs

The increasing complexity of advanced points to a future filled with digital twins, virtual fabrication platforms, and connected simulation ecosystems. These technologies offer the potential to revolutionize the way packages are designed, manufactured, and tested. Engineers can run virtual scenarios to optimize materials, placement, and bonding conditions, long before altering any line parameters physically. This proactive approach reduces trial-and-error in the fab, minimizing disruptions and speeding time-to-market.

“Promex monitors state-of-the-art metrology technology and continues to make investments in these tools to support high-complexity assembly,” said Fromm. “Innovation in characterization tools is rapidly enabling improved in situ measurements of key parameters with increasing automation. These technologies are the engines that improve yield and increase quality during manufacturing and in the field.”

By integrating these measurement tools with AI-driven analytics, digital twins can simulate the entire manufacturing line’s response to changes. As data accumulates, virtual models become more accurate, guiding strategic decisions about material substitution, process adjustments, or design modifications. For instance, if a digital twin predicts that a specific bonding process will result in excessive warpage, engineers can explore alternative bonding techniques or modify the package design to mitigate the issue.

The concept of a virtual fab takes this a step further by creating a complete virtual representation of the entire manufacturing facility. This allows engineers to simulate the flow of materials, the operation of equipment, and the interaction of different processes. By analyzing the data generated by the virtual fab, engineers can identify bottlenecks, optimize resource allocation, and improve overall manufacturing efficiency.

The use of AI-driven process control also is becoming increasingly important in advanced packaging. These systems can analyze real-time data from metrology tools to detect and correct process variations before they lead to defects. This allows for tighter control of process parameters and reduces the need for manual intervention.

The payoff for those who master predictive precision needs is substantial. Stable yields, reliable performance, and predictable timelines translate into better profitability and stronger competitive positioning. In an industry where a single deviation can derail an entire product line, predictive precision serves as both a protective measure and a key differentiator.

Conclusion

As complexity intensifies and advanced packaging strategies evolve, precision remains central to the industry’s progress. Achieving and maintaining precision for manufacturing advanced packaging is the product of collective effort — cross-disciplinary teams, sophisticated tools, rigorous methodologies, and ongoing collaboration across the supply chain.

Data-driven analytics, machine learning, virtual fabrication, and standardized practices all converge on a single objective — to ensure that every component in a multi-die, multi-material assembly meets its specifications, consistently and reliably. Those who invest in these capabilities now will set the standard for future technologies, defining how advanced packaging scales and how the semiconductor industry continues to innovate. In this environment, mastering precision in your manufacturing process transforms from a technical hurdle into a strategic advantage.

Related Reading

Yield Management Embraces Expanding Role

From wafer maps to lifecycle management, yield strategies go wide and deep with big data.