Di chuyển IC tương tự bằng AI

My first job out of college was migrating a DRAM chip from one process node to a newer node, and it was a 100% manual process that required many months of effort. That need to migrate semiconductor IP to newer nodes is still with us today, and much automation has been applied to digital circuits, however migrating analog IP has proven to be much more challenging to automate. I spoke with Girish Vaidyanathan, Product Management Director at Cadence to learn how their Virtuoso Studio tools were enabling AI-driven, custom design migration.

IC design companies want higher productivity, and faster turnaround time to enable the promises of IP design reuse as they move from one node to a newer node, staying within the foundry partner ecosystem or even moving to another foundry. Ideally, during an IP migration the design intentions should remain the same, for example, matching and shielding requirements. Any automation for migration needs to understand the design intents, while at the same time conforming to the new PDK being targeted.

Early migration approaches with older nodes used more of a Lambda scaling when process nodes were at 180nm or larger dimensions, but today each new process generation doesn’t scale with Lambda, so the non-uniform scaling of transistors, interconnects, contacts and vias requires a much smarter approach to migration. The IC layout approaches dramatically change when migrating from planar to FinFET, and FinFET to GAA.

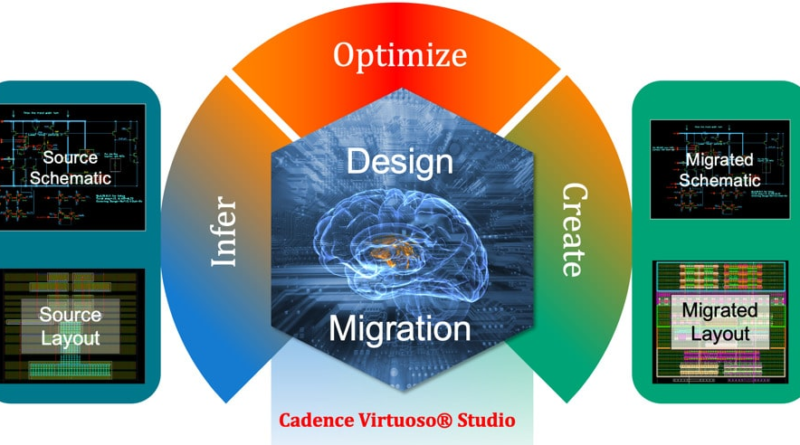

What Cadence has put together in Virtuoso Studio is an AI-powered flow that accepts schematic and layout as inputs, infer the design intentions, apply mapping from the foundry source to target, transform the source schematic to a target schematic, optimize the parameters of the devices to make the circuit meet the target specifications, and automates the layout migration process.

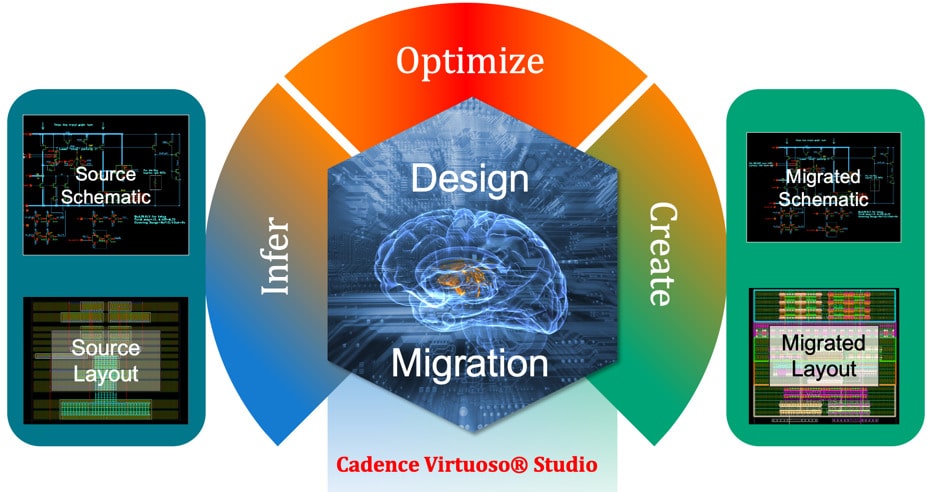

The schematic migration flow is shown in more detail in the customer presentation at Cadence Live:

A testbench from the Virtuoso ADE Suite is rerun to see if the specifications are met, and optimizations are run after updating parameters to meet the new specifications. The optimization helps meet the specifications across all PVT corners. ML techniques are used to infer optimizations. The design space is too large for analog designs, so non-gradient based techniques are used for optimizations. ML techniques are also applied during the creation of the new layout.

I learned that during circuit simulation in this optimization flow you can use Cadence or other SPICE circuit simulators. Your CAD team can even use a custom optimizer in the flow by coding in C++ or Python. There’s the Virtuoso ADE framework to manage circuit simulations, so you can use the Cadence optimizer or your own. Cadence developers have spent the last three years on this automated migration flow. You can even have Cadence do an IC migration for your project, as a service option.

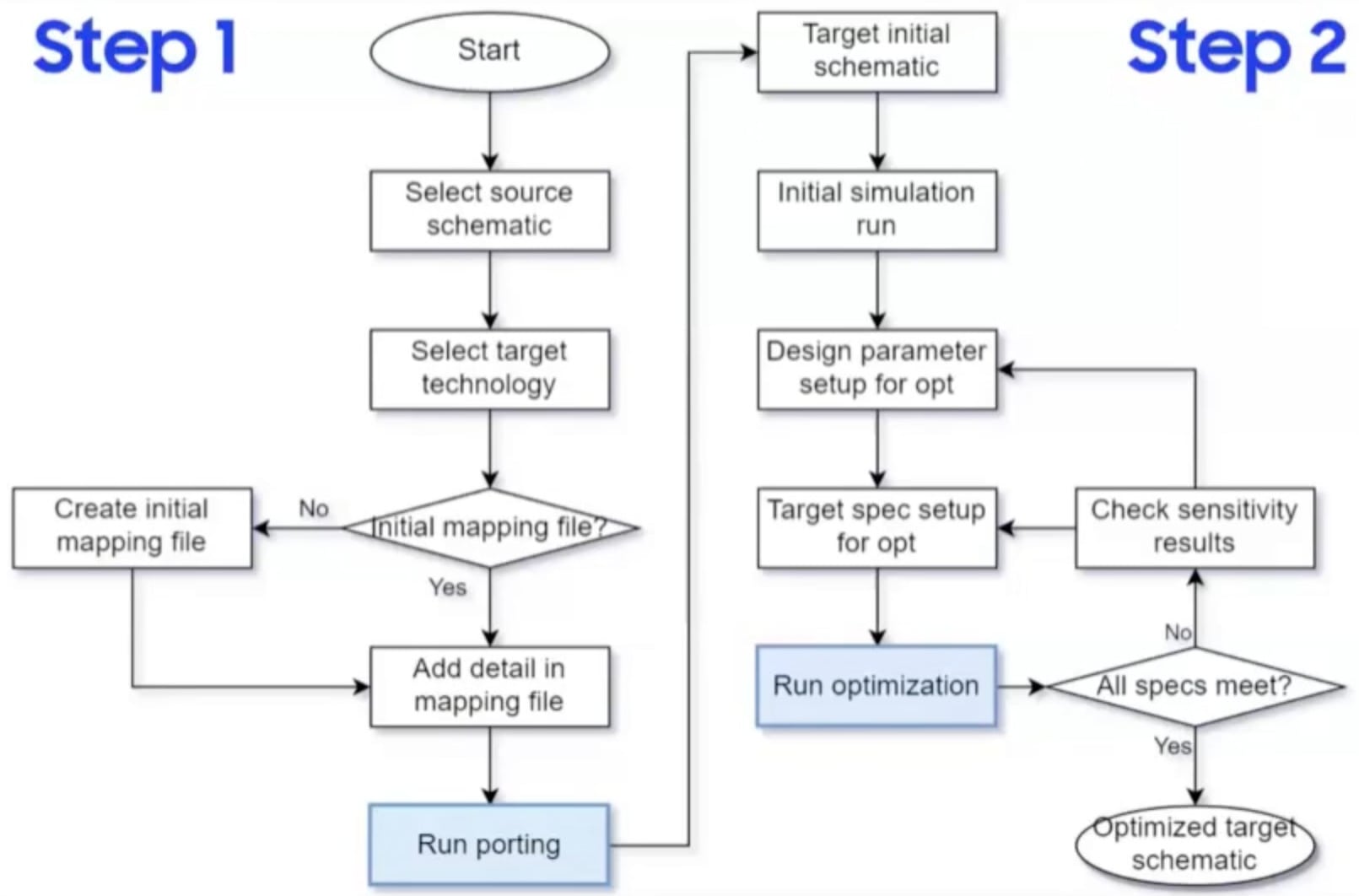

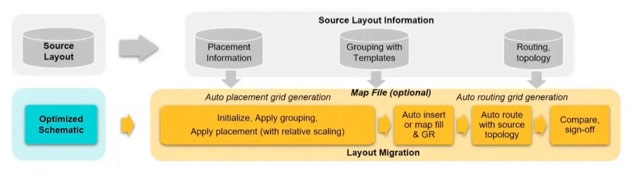

The layout migration flow is shown below and has several steps where you guide the tool to get the best results that meet specifications:

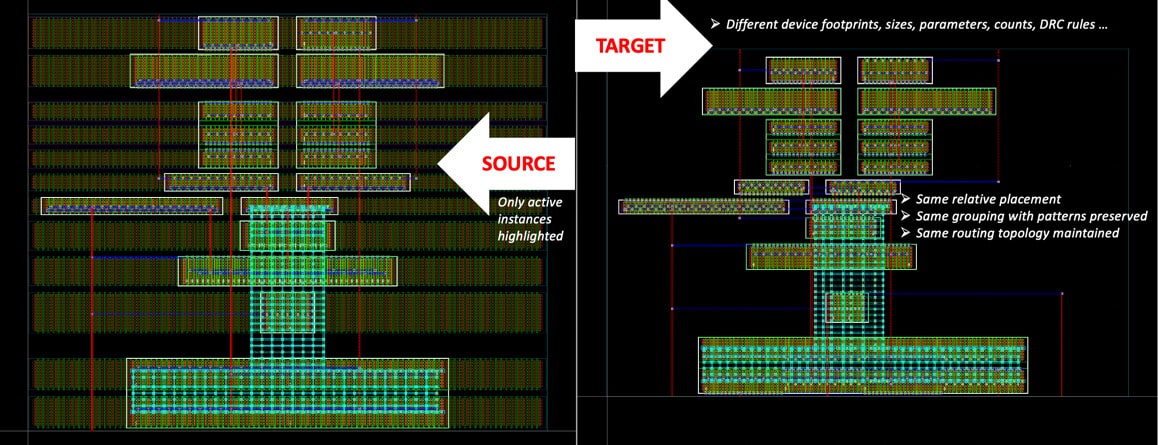

Girish showed me a sample analog layout that was migrated using Virtuoso Studio where automated place and route demonstrated a 2X productivity gain over manual methods:

For Cadence customers there are four interesting videos from CadenceLIVE events that highlight several use cases for analog IC migration:

- Samsung – schematic migration

- Global Foundries – schematic migration, AI/ML-driven optimization, layout migration

- TSMC – RF migration

- Intel – layout migration

Summary

Migrating custom and analog IP is a challenging engineering task that can be done either manually or with the help of automation. Cadence has created an automated migration flow that is producing some impressive results in saving time and reducing engineering effort by using ML-based optimization in the flow. Major customers have already been using the flow, so it’s safe to give it a look for your own migration projects

Related Blogs

Share this post via: