Đánh giá blog: Ngày 9 tháng 10

ECAD-MCAD collaboration; AXI4 locking mechanism; SRAM PUF; ADAS challenges; gate resistance; Gemini AI’s network comms.

Siemens’ Stephen Chavez looks at the key benefits and challenges to achieving a successful ECAD-MCAD collaboration.

Cadence’s Nayan Gaywala shares the AXI4 locking mechanism when implementing an Xtensa LX-based multi-core system on a Xilinx FPGA platform, using a dual-core design mapped to a KC705 platform as an example.

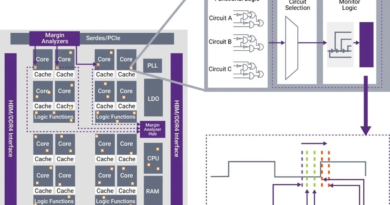

Synopsys’ Vincent van der Leest digs into SRAM PUFs and their role in chip security, taking advantage of naturally occurring variations in silicon manufacturing to generate device-unique cryptographic keys.

Arm’s Guilherme Marshall outlines the challenges of ADAS feature adoption, including lack of platform scalability, software complexity, legacy organizational practices, and global standards and regulations.

Ansys’ Maxim Ershov delves into gate resistance in IC design flows and challenges around parasitic resistance, capacitance, inductance, and more.

Keysight’s Anubhab Sahu shows the background network communications that take place when calling the Gemini AI model’s GenerateContent API, with a detailed look at the decrypted traffic.

Plus, check out the blogs featured in the latest Systems & Design newsletter:

Siemens’ Reetika and Sulabh Kumar Khare show how to accelerate reset domain crossing verification with data analytics techniques.

Keysight’s Ben Miller provides an in-depth look at PAM4, the high-speed data communication standard for pulse amplitude modulation.

Blue Cheetah’s Elad Alon explains how to enable innovative multi-vendor chiplet-based designs for single-vendor, multi-vendor, and plug-and-play markets.

Arteris’ John Min contends the best way to manage performance in modern SoCs is through NoCs because they provide adaptable data paths.

Cadence’s Shyam Sharma looks at different DRAM DIMMs including the DDR5 UDIMM evolution to clock buffered DIMMs (CUDIMM).

Axiomise’s Ashish Darbari and Ia Tsomaia discuss verification, simulation, and corner-case bug hunting for RISC-V.