Cuộc đua đến chất nền thủy tinh

The chip industry is racing to develop glass for advanced packaging, setting the stage for one of the biggest shifts in chip materials in decades — and one that will introduce a broad new set of challenges that will take years to fully resolve.

Glass has been discussed as a replacement material for silicon and organic substrates for more than a decade, primarily in multi-die packages. But with Moore’s Law running out of steam, the shift away from planar chips to advanced packaging is now almost a given for leading-edge designs. The challenge now is how to build these devices more efficiently, and glass has emerged as a key enabler at the leading edge of packaging and lithography. Intel announced last year that it would introduce glass substrates in the latter part of this decade. And the U.S. government awarded Absolics, an affiliate of Korea’s SKC, $75 million under the U.S. CHIPS Act to build a 120,000 square-foot facility in Georgia to make glass substrates.

“The benefits of glass are clear,” says Rahul Manepalli, fellow and director of substrate TD module engineering at Intel. “But the problems that you have to solve include interface stresses, understanding fracture dynamics of glass, and understanding how to decouple stress from one layer to another.”

The brittleness of glass is especially problematic as substrates are made thinner to meet the requirements of modern semiconductor devices. Handling and processing these thin glass substrates requires meticulous care and precision, as the risk of breakage increases significantly.

Glass also makes inspection and metrology more challenging. “We’re transitioning away from smaller fields typical in wafer-based lithography,” says Keith Best, director of product marketing for lithography at Onto Innovation. “When working with glass, mere scaling up isn’t sufficient. It requires a low numerical aperture (NA) lens system capable of achieving the necessary depth of focus across a much larger area without compromising resolution.”

In addition, large foundries and OSATs already have made significant investments in other materials, such as copper clad laminates. Those are field-proven as a base material in PCBs, but they will run out of steam when the packaging industry gets down below 2/2nm lines/spaces. Shifting to glass requires a whole new round of equipment investments and new processes, or some way to combine it with existing processes.

“There is currently no equation that will allow us to create a dedicated line for glass substrates,” says Yin Chang, senior vice president at ASE Group. “There is no business to support that today. It has to either fit into a standard process, or the adoption will take longer.”

Why glass, and why now?

Despite these hurdles, the industry generally acknowledges the transformative potential of glass panels and the high likelihood of its eventual adoption. Glass provides superior dimensional stability, as well as the ability to support a larger area with finer patterning. It also shares the same coefficient of thermal expansion as silicon, and it is extremely flat and stable.

“There’s definitely a trend toward glass,” says Doug Shelton, marketing manager at Canon. “Glass is very forgiving, and it’s got some electrical characteristics that are advantageous. It makes the lithography side easier, as long as they don’t try to go super thin.”

One of glass’ most attractive features is its low dielectric constant, minimizing signal propagation delays and crosstalk between adjacent interconnects, which is crucial for high-speed electronics. It also reduces the capacitance between interconnects, allowing for faster signal transmission and improved overall performance. In applications such as data centers, telecommunications, and high-performance computing, where speed is of the essence, the use of glass substrates can significantly enhance system efficiency and data throughput.

The low dielectric constant also enables better impedance control, ensuring signal integrity across the entire circuit. This is particularly attractive in RF applications, where impedance matching is essential for maximizing power transfer and minimizing signal loss. By providing consistent electrical properties across the substrate surface, glass substrates facilitate the design and fabrication of high-frequency circuits with enhanced reliability and performance.

Another key advantage of glass substrates is exceptional thermal stability, which plays a vital role in maintaining device performance under fluctuating thermal conditions. Unlike copper-clad laminate, which can deform or delaminate under thermal stress, glass substrates exhibit minimal dimensional changes over a wide temperature range. In applications where thermal management is critical, such as automotive electronics, aerospace systems, and industrial controls, glass’ ability to withstand thermal cycling and maintain dimensional integrity under stress helps prevent electrical shorts, opens, or other reliability issues commonly associated with temperature-induced mechanical strain.

“The data-centric world is where we expect glass to be adopted first, with AI/ML-based packages,” says Intel’s Manepalli. “The performance benefits that application immediately.”

The thermal stability of glass substrates also simplifies the design and implementation of advanced packaging solutions, allowing for tighter integration of components and increased packaging density. By eliminating concerns related to substrate warpage or deformation, glass substrates enable more precise alignment of chip components, finer pitch interconnects, and improved overall system performance.

“It will be interesting to see how these glass materials enter the ecosystem of these complex devices, both on the substrate level and within the higher-level integrations,” says David Fromm, COO at Promex Industries.

Process improvements

Another big advantage of glass substrates is its exceptional flatness, which is critical for panel-level lithography processes, where precise alignment and uniformity of features are essential for achieving high-resolution patterning. Glass substrates ensure consistent focal plane alignment during lithography, enabling the creation of fine-pitch interconnects and intricate circuit patterns with superior accuracy and reproducibility.

Moreover, the flatness of glass substrates enhances the yield and reliability of semiconductor devices by minimizing the occurrence of such defects as pattern distortion or misalignment. That, in turn, results in higher manufacturing yields and improved overall device performance, particularly in applications requiring tight tolerances and high levels of integration.

Transitioning to glass also supports process flows. With its predictable behavior under a range of processing conditions, glass minimizes process variables. Engineers can fine-tune their processes around a material that responds reliably and consistently, improving efficiency and predictability in production lines — once the handling issues are resolved.

“Glass panel processing requires meticulous precision,” adds Best. “But once you’ve nailed down your process, the material works with you, not against you.”

A significant challenge in lithography for glass substrates is their inherent fragility, which becomes particularly pronounced as the industry moves towards thinner substrates to accommodate the demands for higher device integration and performance. Thin glass panels, often reaching thicknesses of 100µm or less, presenting substantial risks during handling and manufacturing processes. The susceptibility of glass to cracking or shattering under stress underscores the need for specialized equipment and processes tailored to safely manage the material.

“Glass substrates have their own sets of challenges,” says Brad Perkins, product line director at Nordson Test & Inspection. “When you look at a 500-plus millimeter square for those large glass panels, you run into some real challenges with how much that bends and warps, and then how do you hold them?”

Addressing this fragility requires handling systems to match the sophistication of lithography technology itself. Advanced packaging companies are actively exploring robust handling, vacuum, and mechanical support systems to transport and process these delicate glass panels without breakage. Furthermore, innovations in soft handling techniques for loading and unloading substrates from lithography equipment are being pursued to mitigate the risks associated with handling fragile glass substrates.

“Thin glass substrates are extremely delicate and require careful handling,” says Onto’s Best. “It demands finesse, precision, and, above all, innovation in handling techniques. You have to move it around very gingerly. For instance, when you put it in an electroplating bath, the agitation and turbulence of the bath can shatter it.”

Hybrid substrates

Glass also can be combined with the traditional substrates, allowing existing approaches to capitalize on the thermal stability and electrical advantages of glass while leveraging the mechanical robustness and well-established manufacturing practices of materials, such as organic laminates or silicon interposers. The outcome is a substrate with superior overall performance metrics capable of meeting the diverse demands of contemporary and future chip designs.

For example, a hybrid substrate might feature a glass core for low-loss, high-frequency signal transmission, layered with copper clad laminate (CCL) to enhance structural rigidity and cost-effectiveness. This synergistic combination could mitigate some of the challenges associated with glass, such as brittleness, while harnessing its high-performance characteristics.

“Marriage of glass with other substrates isn’t merely about amalgamating the best of both worlds,” says Onto’s Best. “It’s about attaining performance characteristics we’ve never before witnessed.”

Standardization and compatibility

A significant hurdle facing the adoption of glass panels is the absence of a unified standard for glass substrate size, thickness, and properties. Unlike silicon wafers, which adhere to precise global specifications, glass substrates currently lack universally accepted dimensions and characteristics. This deficiency in standardization complicates matters for equipment manufacturers striving to produce universally compatible tools, and for semiconductor fabs seeking to interchange substrates without significant adjustments to their processes.

Closely linked to standardization is the issue of compatibility, not only among different batches of glass substrates, but also between the substrates and the semiconductor devices they support. Careful matching of glass’ unique electrical and thermal properties with those of the semiconductor devices is imperative.

“You’re not going to use glass on a mature product,” adds ASE’s Chang. “It’s going to be on the most advanced applications with better power solutions. But it will be harder to handle. That is one of its key issues.”

As the semiconductor industry progresses toward advanced packaging methods, such as chiplets and 3D-ICs, a notable transformation is unfolding in back-end processes. This shift involves the adoption and adaptation of methodologies traditionally linked with front-end semiconductor manufacturing.

Lithography now plays a pivotal role in creating line pitches below 2µm that are necessary for the adoption of chiplets and 2.5D/3D-IC packaging. But these finer dimensions also require materials capable of withstanding tighter processing conditions while maintaining structural and functional integrity.

“The big challenge we’re facing right now is getting the most we can out of lithography tools,” says Travis Brist, senior product marketing manager for Synopsys. “While there’s always been a push to do that, it’s becoming more critical.”

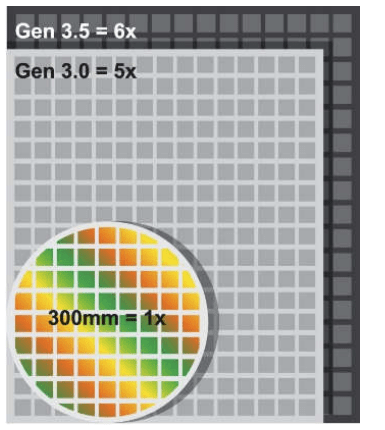

With fewer restrictions on substrate format in packaging, and the ability to use a bigger lens with lower numerical aperture, packaging vendors are moving to fan-out panel-level packaging (FOPLP) to process more packages per panel thus reducing costs. It’s estimated that a 30% to 40% cost reduction for panels can be achieved relative to a round 300mm wafer fan-out. [1]

Fig. 1: Panel-level packaging offers a significant increase in die as a function of substrate size. Source: Onto Innovation

Innovations

Given the larger size and different physical properties of panels compared to silicon wafers, achieving the fine-pitch interconnections necessary for advanced packages requires lithographic techniques that can produce smaller feature sizes in panel substrates without compromising on alignment accuracy. This is particularly challenging on larger panels, where warpage becomes an issue and must be accounted for during the lithography process.

Copper clad laminate (CCL) has been the go-to substrate material for FOPLP due to its durability, robust mechanical properties and cost-efficiency. Its composition makes it a durable choice for the rigors of semiconductor packaging processes, and the relative affordability of fiberglass and copper contributes to its widespread adoption.

But the structure of CCL, which contributes to its strength, also makes it susceptible to warping under the thermal and mechanical stresses typical in FOPLP. Each layer of the substrate may produce slightly different overlay deviations, a complication arising from the distortion of the panel. Such deviations are critical to control, as they can lead to challenges in maintaining consistent line patterns and feature sizes. Even minor discrepancies can lead to substantial yield losses and impact the overall efficacy of the packaging.

In addition, minute variations in CCL’s electrical properties across the substrate surface can affect signal integrity and overall device performance, especially in high-frequency applications.

“Copper clad laminate is very robust, but when it comes to warpage and distortion, it is very unstable,” says Onto’s Best. “But CCL is where most people are playing today. They’re getting 9/12 [nm line/space] and thinking about maybe getting to 5/5. Some people even want to push it to 2/2, but that’s probably the end for CCL. Then there’s the race to get to glass.”

Compatibility extends beyond the physical properties of glass to encompass the adhesion of other materials used in the semiconductor stack, such as dielectrics and metals, which may behave differently on glass compared to traditional substrates.

In the absence of industry standards, performance variability also emerges as a common challenge. With each manufacturer adhering to its proprietary specifications for glass substrates, a situation arises where one company’s product may not perform identically to another’s, even for the same application.

As advanced packaging progresses toward finer pitches and more intricate interconnect technologies, disparities in thermal expansion coefficients and electrical properties between glass and other materials in the stack become increasingly critical. Without standardization, the integration of glass with technologies such as through-glass vias (TSVs) and microbumps becomes fraught with complications, potentially impacting yield and reliability.

Addressing these challenges necessitates industry-wide collaboration to develop and adopt standards for glass substrates. Such collaboration involves working groups comprised of glass manufacturers, semiconductor companies, packaging specialists, and equipment vendors, all contributing to the establishment of reliable standards that enhance predictability and efficiency in manufacturing processes.

Standardization and compatibility will be paramount as glass substrates aspire to play a pivotal role in the future of advanced packaging. Only through industry collaboration and agreement on common protocols can the full benefits of glass substrates be realized.

Conclusion

With glass panels, manufacturers can push the boundaries of interconnect density, paving the way for more complex and tightly integrated circuits. Devices become not only smaller and faster but also more reliable due to the uniformity of electrical properties across the substrate, ensuring consistent device performance batch after batch.

“There is so much more that you can do with glass, and we haven’t even scratched the surface,” adds Manepalli. “We aren’t even using glass for its high frequency benefits yet. Imagine the things you can create with glass and its advantageous properties once we get the process figured out.”

Reference

1. K. Best, G. Singh and R. McCleary, “Advanced packaging lithography and inspection solutions for next generation FOWLP-FOPLP processing,” 2016 17th International Conference on Electronic Packaging Technology (ICEPT), Wuhan, China, 2016, pp. 1090-1094, doi: 10.1109/ICEPT.2016.7583315.

Related Reading

Glass Substrates Gain Foothold In Advanced Packages

Problems need to be solved before this technology goes mainstream, but the benefits are significant.