Chuẩn bị cho các thiết bị điện sắt

The discovery of ferroelectricity in materials that are compatible with integrated circuit manufacturing has sparked a wave of interest in ferroelectric devices.

Ferroelectrics are materials with a permanent polarization, the direction of which can be switched by an applied field. This polarization can be used to raise or lower the threshold voltage of a transistor, as in FeFETs, or it can change the tunneling resistance of a junction, as in ferroelectric tunnel junctions (FTJs). More conventional DRAM designs also can exploit ferroelectricity to change the dielectric constant of the storage capacitor. The materials science of ferroelectricity — how properties depend on composition, crystal structure, and processing — plays a critical role in all of these applications. For ferroelectric devices to become commercially viable, the industry needs improved understanding of these relationships.

Ferroelectrics and DRAM

DRAMs, like CMOS devices, face tension between the need to reduce dielectric thickness and the need to minimize leakage current. Increasing the dielectric constant of storage capacitors can help manage this balance.

Ferroelectric hafnium zirconium oxides (HZO) offer high dielectric constants and acceptably low leakage current. However, while hafnium oxide gate dielectrics are amorphous, the properties of HZO are tied to the material’s crystal structure. To successfully scale HZO dielectrics, manufacturers need nanometer-scale structure control, a difficult processing challenge.

In perovskite ferroelectrics like PbZrO3-PbTiO3 (PZT), the crystal structure is primarily determined by the composition. In a review, Minhyun Jung and colleagues at Korea Advanced Institute of Science and Technology (KAIST) explained that perovskites follow an ABO3 pattern, where the A atomic site hybridizes with an oxygen ion to stabilize the ferroelectric behavior.[1] The B atom affects the energy difference between the rhombohedral and tetragonal crystal phases. HfO2 and ZrO2, in contrast, have a fluorite structure, AB2. Ferroelectricity comes from tension on the a-axis of the crystal due to movement of the ions.

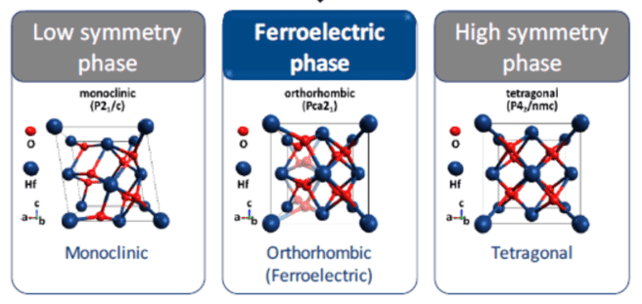

At high Hf concentrations, the equilibrium phase is monoclinic, they said, with para-electric behavior. At high Zr concentrations and high temperatures, an antiferroelectric tetragonal phase appears. The orthorhombic ferroelectric phase is seen between these two extremes, but film thickness, temperature, and the presence or absence of an electric field will all affect phase transitions.

Fig. 1: Unit cells of monoclinic, ferroelectric, and tetragonal phases of hafnium oxide. Source: FMC

When HZO is used in DRAM storage capacitors, the goal is to maximize the dielectric constant, not necessarily the polarization. According to Jung, this maximum dielectric constant occurs near the morphotropic phase boundary (MPB), which lies between the tetragonal and orthorhombic phase. At the compositional boundary between the two, about Hf0.3Zr0.7O2, the energy barrier preventing a phase transition is very low. An electric field is sufficient to switch the material between ferroelectric and anti-ferroelectric behavior. Both the dielectric and piezoelectric constants increase sharply.

Oxygen vacancies and ferroelectric memories

In contrast, ferroelectric memories like FeFETs and ferroelectric tunnel junctions (FTJs rely on ferroelectric polarization. FeFETs, for instance, use a ferroelectric in series with a conventional dielectric as the gate capacitor. The ferroelectric polarization acts as a permanent gate bias, either positive or negative depending on the polarization state. This bias either raises or lowers the threshold voltage. The memory window, the difference between the Vtlo and Vthi values, increases with the polarization density of the ferroelectric.

Typically, thin HZO layers are deposited by ALD, using HfO2, ZrO2, and H2O precursors. To control the composition and resulting crystal structure, manufacturers vary the ratio of precursor cycles. In work presented at last December’s IEEE Electron Device Meeting, Pengfei Jiang and colleagues at the Chinese Academy of Sciences found that a 6:6 Hf:Zr cycle ratio gave the largest initial polarization.[2] Tetragonal phase ZrO2 nuclei helped encourage formation of the ferroelectric orthorhombic phase. The HF:Zr ratio is not the whole story, though. Oxygen vacancies — unoccupied lattice sites where an oxygen atom should be — can have a dramatic impact on the properties of both fluorite and perovskite materials. Sergiu Clima and colleagues at imec explained that oxygen vacancies break local symmetry, changing the kinetic barriers to carrier movement and phase transformations.[3]

More recently, Zeifu Zhao and colleagues at the Beijing Institute of Technology found that a low oxygen vacancy concentration favors the orthorhombic phase, while a high concentration favors formation of the tetragonal phase.[4] Unsurprisingly, oxygen plasma annealing reduced the concentration of oxygen vacancies. However, plasma annealing can cause surface damage, as well. Instead, another group at KAIST used a relatively low annealing temperature, but high pressure, allowing the ferroelectric phase to form with less surface damage and a thinner interlayer.[5]

The interface between HZO and the underlying material is often a source or sink for oxygen. Bong Ho Kim and other researchers at KAIST observed that an interfacial SiO2 layer is inevitable when HZO is deposited on silicon. Silicon dioxide’s lower dielectric constant relative to HZO leads to a capacitive voltage drop and high electrical stress at the interface. The resulting interface degradation can be an even more severe contributor to device fatigue than degradation of the ferroelectric. In FeFET devices, Bong Ho Kim’s group found that introducing an additional high-k layer to avoid voltage drop can reduce the memory window or degrade charge retention. Instead, they incorporated titanium into their FeFET gate metal stack. The titanium scavenged excess oxygen, reducing the interlayer thickness from 1.2 nm down to 0.3 nm.[6]

The deposition substrate also serves as a template for HZO crystallization. Zhao explained that because cubic TiN has a large lattice mismatch with orthorhombic ZrO2, amorphous TiN actually makes a better underlayer. Since the crystallinity of TiN decreases with thickness, thinner layers are preferred. Moreover, using CMP to create a flat deposition surface gave better HZO films with higher breakdown fields.

Defects and device reliability

Devices that depend on ferroelectric switching typically need a “wake-up” cycle to activate the ferroelectric material. Though thinner layers are desirable because they are easier to switch in general, they also tend to require higher wake up voltages. A Taiwanese group used both experimental and modelling studies to find the cause of wake up behavior in FTJs, where carrier tunneling depends on the ferroelectric polarization direction.[7] In the as-manufactured device, they found that trapping and de-trapping in the interfacial layer prevents carriers from reaching the ferroelectric, inhibiting switching. Once sufficient charge accumulates, soft breakdown of the interfacial layer removes this inhibition. Device behavior then reflects the ferroelectric alone. In thinner devices, the interfacial layer is proportionally thicker, and so the wake up effect is more severe.

Because oxygen vacancies serve as charge traps, they also play an important role in device endurance and memory retention. Oxygen vacancies at the interfaces between the ferroelectric and other materials are especially important contributors to trapping behavior. Vacancies generated in the bulk material need time to migrate to the interface. Because of this, Guan Feng and colleagues at Fudan University argued that neither endurance nor retention testing adequately measures ferroelectric capacitor performance in read-intensive applications.

Typical endurance testing uses continuous read/restore cycles, where a capacitor is read, immediately restored, and then read again. Retention testing measures the maximum time between a restore operation and the next successful read. The Fudan University group also measured the duty cycle, or the number of read/restore operations in a given amount of time. They found that smaller duty cycles — corresponding to longer delays between read/restore operations — led to earlier and more rapid degradation. They hypothesized that the longer time between pulses allowed more time for vacancy migration.[8]

Conclusion

The collaboration between engineers and materials scientists is always an important part of the integrated circuit manufacturing enterprise, but especially so as new devices emerge from laboratories and progress toward commercial viability. Recent developments in ferroelectric memories highlight the ways in which fundamentals like crystal structure and interface defects support such prosaic concerns as endurance and retention.

- Jung, M., Gaddam, V. & Jeon, S., “A review on morphotropic phase boundary in fluorite-structure hafnia towards DRAM technology.” Nano Convergence 9, 44 (2022). https://doi.org/10.1186/s40580-022-00333-7

- P. Jiang et al., “A 256 Kbit Hf0.5Zr0.5O2-based FeRAM Chip with Scaled Film Thickness (sub-8nm), Low Thermal Budget (350oC), 100% Initial Chip Yield, Low Power Consumption (0.7 pJ/bit at 2V write voltage), and Prominent Endurance (>10^12),” 2023 International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2023, pp. 1-4, doi: 10.1109/IEDM45741.2023.10413844.

- S. Clima et al., “First-Principles Perspective on Poling Mechanisms and Ferroelectric/Antiferroelectric Behavior of Hf1-xZrxO2 for FEFET Applications,” 2018 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2018, pp. 16.5.1-16.5.4, doi: 10.1109/IEDM.2018.8614552.

- Z. Zhao et al., “Engineering HZO by Flat Amorphous TiN with 0.3nm Roughness Achieving Uniform c-Axis Alignment, Record High Breakdown Field (~10nm HZO), and Record Final 2Pr of 56 μC/cm2 with Endurance > 4E12,” 2024 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits), Honolulu, HI, USA, 2024, pp. 1-2, doi: 10.1109/VLSITechnologyandCir46783.2024.10631450.

- V. Gaddam et al., “Low-Damage Processed and High-Pressure Annealed High-k Hafnium Zirconium Oxide Capacitors near Morphotropic Phase Boundary with Record-Low EOT of 2.4Å & high-k of 70 for DRAM Technology,” 2024 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits), Honolulu, HI, USA, 2024, pp. 1-2, doi: 10.1109/VLSITechnologyandCir46783.2024.10631348.

- B. H. Kim et al., “IL Scavenging and Recovery Strategies to Improve the Performance and Reliability of HZO-Based FeFETs,” 2023 International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2023, pp. 1-4, doi: 10.1109/IEDM45741.2023.10413731.

- C. -Y. Cho et al., “Wake-Up of Ultrathin Ferroelectric Hf0.5Zr0.5O2: The Origin and Physical Modeling,” 2023 International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2023, pp. 1-4, doi: 10.1109/IEDM45741.2023.10413877.

- G. Feng et al., “Comprehensive Analysis of Duty-Cycle Induced Degradations in HfxZr1-xO2-Based Ferroelectric Capacitors: Behavior, Modeling, and Optimization,” 2024 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits), Honolulu, HI, USA, 2024, pp. 1-2, doi: 10.1109/VLSITechnologyandCir46783.2024.10631494.

Related Reading

Ferroelectric Memories Answer Call For Non-Volatile Alternatives

Researchers target NVMs that are compatible with CMOS logic.