Chất bán dẫn 2D đang tiến triển, nhưng Silicon cũng vậy

Semiconductor industry researchers have been anticipating the need for better transistor channel materials to replace silicon for a long time, but silicon devices have continued to improve enough to postpone that change.

Silicon continues to provide an unmatched combination of device performance, manufacturability, and cost effectiveness. In recent years, though, the “end of silicon” channels has become much more likely. Transistors need thinner channels to maintain adequate electrostatic control, but surface scattering causes sharp increases in channel resistance as the thickness drops below three nanometers.

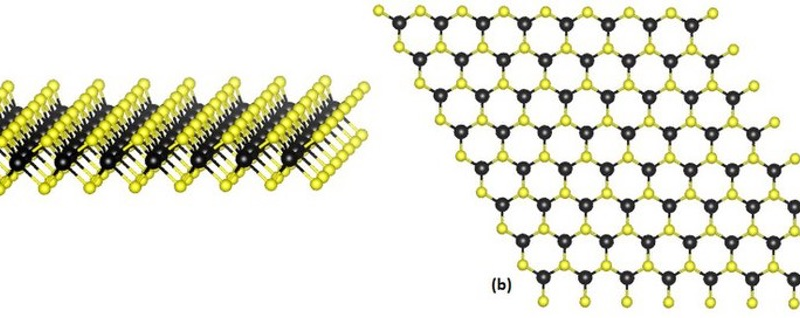

Two-dimensional semiconductors appear to be the most likely alternative. They have no out-of-plane dangling bonds, which minimizes surface scattering. Transition metal dichalcogenides (TMDs), in particular, form crystals with a transition metal such as tungsten or molybdenum sandwiched between layers of sulfur, selenium, or another chalcogen. TMDs have made significant progress over the last several years in the lab, but they face significant hurdles ahead with respect to material growth, integration, and manufacturing.

Fig. 1: Crystal structure of a monolayer of transition metal dichalcogenide. Source: Wikimedia Commons

Silicon channel development is not standing still, of course. Gouri Sankar Kar, vice president of R&D at imec, noted in an interview with Semiconductor Engineering that CFET architectures, which place PMOS and NMOS transistors in a single vertical structure, potentially can extend silicon scaling for as long as two more decades. Furthermore, Kar noted that it isn’t enough for an alternative channel material to match silicon’s performance, or even slightly improve on it. A proposed silicon replacement must also be able to match silicon’s manufacturability and cost. 2D materials still have a long way to go to achieve cost parity.

First, make high quality crystals

To adopt an alternative channel material, manufacturers first have to be able to make it.

Fabs need consistent quality over the area of a 300mm wafer. For a long time, the best 2D semiconductor devices, by a wide margin, used exfoliated flakes from bulk material. Though the best CVD films can now match flake performance, CEA-Leti research engineer Lucie Le Van-Jodin explained that they are grown at temperatures above 600°C, on substrates like sapphire and quartz. Even with seed layers, good quality growth on arbitrary substrates is not yet possible. Films grown at more moderate temperatures tend to have much smaller grains.

Layer transfer from a growth wafer to a target wafer is a well-established process. With 2D semiconductors, though, the layer being transferred is only three atoms thick. Wrinkles, voids, and other defects can degrade film quality. In work presented at this year’s VLSI Symposium, S. Ghosh and colleagues at imec reduced transfer-related defects through careful optimization of the bond front. Still, adhesives used in the transfer process leave carbon residue that can be difficult to remove without damage.[1]

Meanwhile, work reported by Intel found that sub-threshold swing performance — about 88 mV/decade in Intel devices — was dominated by carbon contamination.[2] Reducing the dielectric thickness did not improve their results.

It’s not strictly necessary to cover the entire area of the wafer with 2D semiconductor, just the transistor channels. That’s the idea behind selective growth approaches. Typically selective growth of 2D semiconductors starts by depositing and patterning a seed material such as metallic tungsten or Al2O3, according to Guixu Zhu and colleagues at the University of Science and Technology of China.[3] The 2D material preferentially deposits on the seed layer, rather than the surrounding SiO2. On unpatterned substrates with the same CVD parameters, this group achieved 96.2% MoS2 coverage on Al2O3, compared to 10.8% coverage on SiO2. They then used patterned Al2O3 triangles as nucleation sites for MoS2 growth. The resulting material had mobility as high as 62.8 cm2/V-sec, though with a mean mobility value of only 43 cm2/V-sec.

Still, in remarks at this year’s Materials Research Society Spring Meeting in Seattle, Kevin O’Brien, a principal research engineer at Intel, pointed out that even “good” results demonstrate a level of variability that terrifies process engineers. The expected number of grain boundaries in a silicon transistor is zero. The expected sub-threshold swing for a leading edge silicon transistor is approaching 60 mV/decade, the theoretical limit. While champion devices from laboratory research are promising, O’Brien said that 2D semiconductors are simply not manufacturable without better and more consistent film quality.

Second, make contacts and gate dielectrics

Current 2D materials may not be ready for prime time, but they are good enough to enable deeper exploration of device integration issues. One of the most serious is the need for reliable, low-resistance contacts. Like the channel length, contact length needs to scale with the device gate pitch. According to Wen-Chia Wu and colleagues at TSMC, contact resistance increases sharply as contact length drops below about 10nm, transitioning from ohmic to Schottky-like behavior.[4] In earlier work, the same group identified the transfer length — the distance over which channel current drops to 10% of its baseline — as a key parameter in limiting contact resistance.[5] The transfer length in turn strongly depends on the tunneling distance at the contact/channel interface. Regardless of the process scheme or the material used, Wu said that good quality contacts depend on very clean, very smooth interface surfaces. Ohmic behavior and a short transfer length imply a need for van der Waals contacts, in which there is a clear separation between the contact metal and the semiconductor.

CEA-Leti’s Le Van-Jodin noted that the most successful contact metals are bismuth, antimony, and indium, all of which are new to integrated circuit manufacturing and all of which have relatively low melting points. And in work reported by Ang-Sheng Chou, another TSMC group found that with antimony contacts to MoS2 transistors, both channel and contact resistance depended on the carrier density induced by the gate voltage.[6] Device designers would much prefer contacts with fixed doping and a stable resistance value, but that problem is so far unsolved.

Depositing a reliable gate stack, like contact formation, is challenging because the 2D material surface provides very few nucleation sites. Most device demonstrations so far place the 2D material on top of a pre-fabricated bottom gate structure. Wouter Mortelmans, a research engineer at Intel, pointed out that a gate-all-around design with symmetric top and bottom gates is more commercially realistic. Their best results from such a design offered a sub-threshold swing of 86 mV/decade with a 34-nm gate length. As with contact formation, effective surface cleaning and carbon residue removal are critical.

Commercially viable devices also require patterning. Laboratory studies tend to involve, at most, a few dozen devices widely distributed on the substrate, not the millions of densely packed transistors seen in modern integrated circuits. Le Van-Jodin observed that 2D materials generally are not strongly adhered to the underlying substrate, whatever it is. Wet etch processes risk delaminating them. Plasma etching risks surface damage, and the protective etch “polymer” that typically protects surfaces in silicon CMOS processes is difficult to remove. Depositing a protective oxide layer first, then patterning the combined stack offers one potential solution.

Next, applications — maybe

Improvements in film quality, contact quality, gate oxide deposition, and patterning still don’t lead to complementary logic. PMOS and NMOS devices depend on different channel materials, most commonly WSe2 for PMOS, and MoS2 or WS2 for NMOS. While it might be possible to create CFET-like structures with the two devices stacked vertically, putting PMOS and NMOS devices side-by-side is extremely difficult.

Considering the obstacles to successful 2D semiconductor CMOS channels, it’s just as well that the near-term future of silicon is bright. There is time for the industry to pursue 2D transistor development in less demanding applications. For example, imec’s Kar observed that power circuits account for between 5% and 7% of the total circuit area, and leading-edge designs already envision moving power distribution to the back of the wafer. Using layer transfer to build 2D power switches might be easier than depositing silicon on the backside, and the dimensional requirements for power circuits are less demanding.

In his MRS remarks, O’Brien quoted Wolfgang Pauli: “God made the bulk. Surfaces were invented by the devil.” In 2D materials, there is no bulk. The devilish surfaces they offer look promising, but significant work remains.

References

- S. Ghosh et al., “EOT Scaling Via 300mm MX2 Dry Transfer – Steps Toward a Manufacturable Process Development and Device Integration,” 2024 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits), Honolulu, HI, USA, 2024, pp. 1-2, doi: 10.1109/VLSITechnologyandCir46783.2024.10631364.

- W. Mortelmans et al., “Record Performance in GAA 2D NMOS and PMOS Using Monolayer MoS2 and WSe2 with Scaled Contact and Gate Length,” 2024 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits), Honolulu, HI, USA, 2024, pp. 1-2, doi: 10.1109/VLSITechnologyandCir46783.2024.10631395.

- G. Zhu et al., “Single-Crystalline Monolayer Mos2 Arrays Based High-Performance Transistors via Selective-Area CVD Growth Directly on Silicon Wafers,” 2024 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits), Honolulu, HI, USA, 2024, pp. 1-2, doi: 10.1109/VLSITechnologyandCir46783.2024.10631381.

- W. -C. Wu et al., “On the Extreme Scaling of Transistors with Monolayer MOS2 Channel,” 2024 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits), Honolulu, HI, USA, 2024, pp. 1-2, doi: 10.1109/VLSITechnologyandCir46783.2024.10631401.

- W. -C. Wu et al., “Scaled contact length with low contact resistance in monolayer 2D channel transistors,” 2023 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits), Kyoto, Japan, 2023, pp. 1-2, doi: 10.23919/VLSITechnologyandCir57934.2023.10185408.

- A. -S. Chou et al., “Status and Performance of Integration Modules Toward Scaled CMOS with Transition Metal Dichalcogenide Channel,” 2023 International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2023, pp. 1-4, doi: 10.1109/IEDM45741.2023.10413779.