Cập nhật SI và PI từ Cadence trên Sigrity X

Signal Integrity (SI) and Power Integrity (PI) issues are critical to analyze, ensuring the proper operation of PCB systems and IC packages, yet the computational demands from EDA tools can cause engineers to only analyze what they deem are critical signals, instead of the entire system. Cadence has managed to overcome this SI/PI analysis limitation by using distributed simulation, where all of the cores in a machine are used, along with distributing the workload to multiple machines. Sigrity X is the platform from Cadence that uses distributed simulation for SI/PI for PCB and IC package designs.

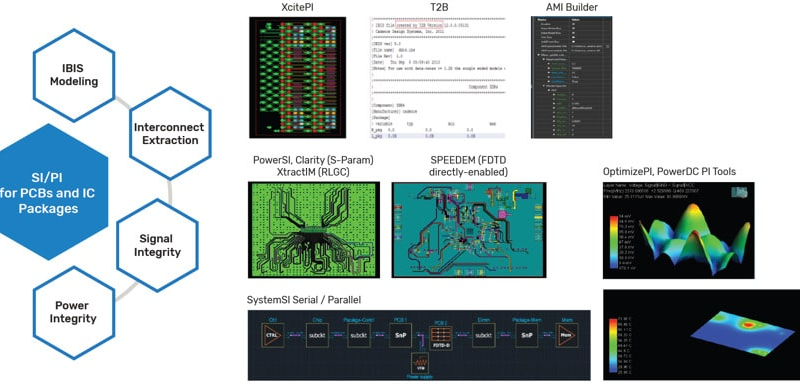

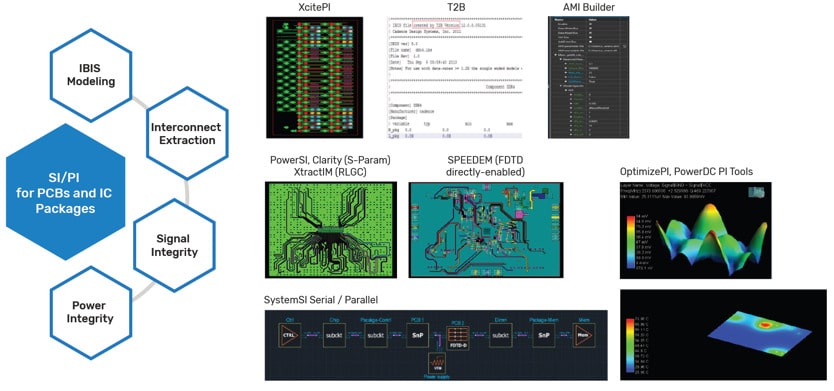

Sigrity entails multiple EDA tools, each aimed at a specific task.

- IBIS Modeling – AMI Builder

- Transistor to Behavioral model conversion – T2B

- Interconnect extraction – XcitePI

- EM field solver – PowerSI, XtractIM

- Serial/Parallel link analysis – SystemSI

- Finite Difference Time-Domain Analysis – SPEEDEM

- Power Integrity – OptimizePI, Sigrity PowerDC

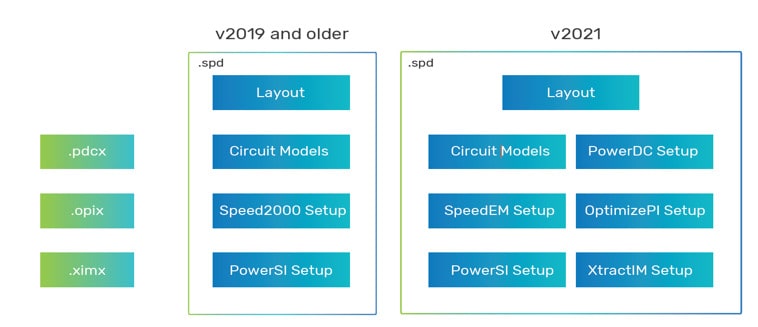

The database used in Sigrity X has migrated into a single .spd file, instead of being spread out over multiple files, simplifying your workflow.

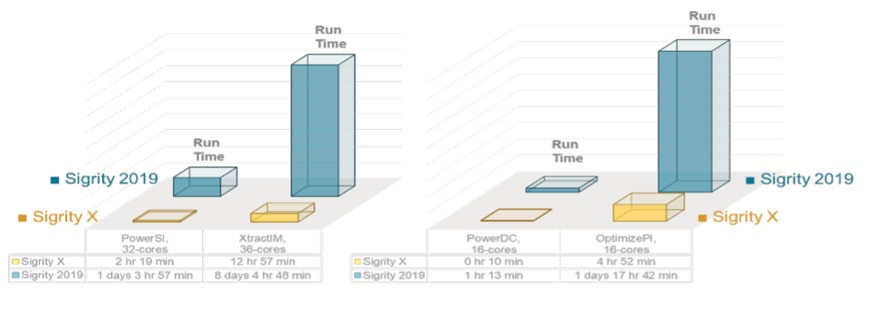

Runtime improvements with Sigrity X are about 10X faster, all with the same accuracy level. For the PowerSI comparison a package plus PCB simulation improved by 12X. With XtractIM run on an InFO package showed a 15.1X speedup. On a FC-BGA package simulation the improvement was 7.18X. OptimizePI simulation was 8.56X faster using Sigrity X.

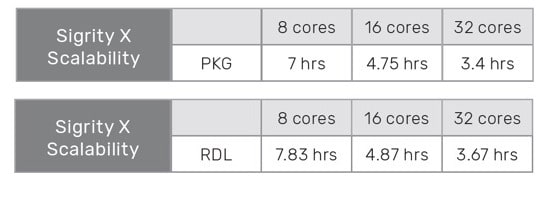

Run times depend on how many cores are used, so here’s a table showing the scalability comparisons. Users decide how many machines and cores to use for each run.

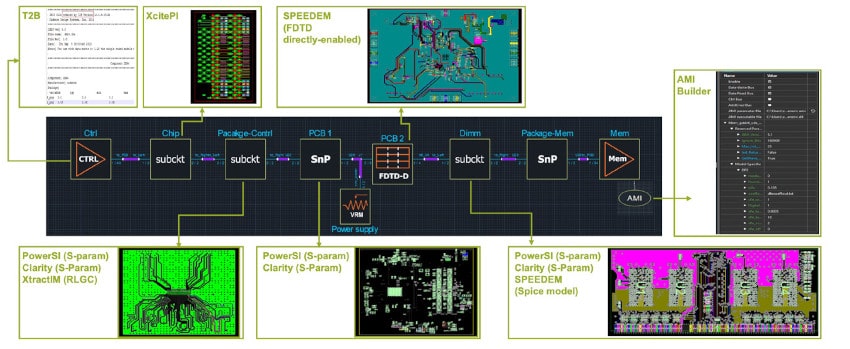

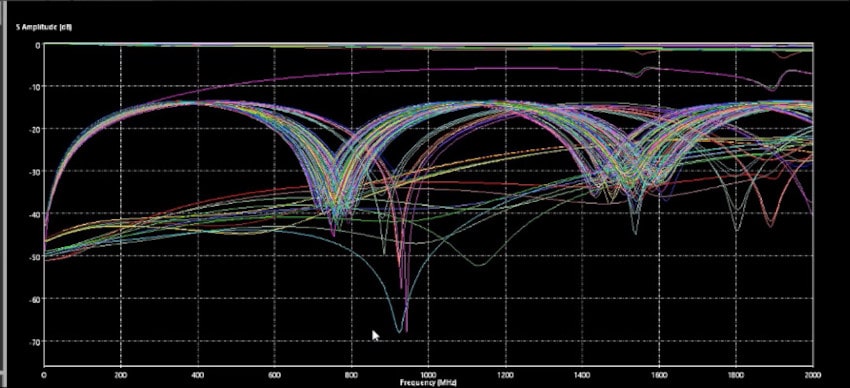

PCB designers using Allegro canvas can run Sigrity analysis for topological extractions, crosstalk and reflections, IR drop, impedance, coupling and return path simulations. For system-level simulations here’s an example flow using Sigrity and Clarity tools.

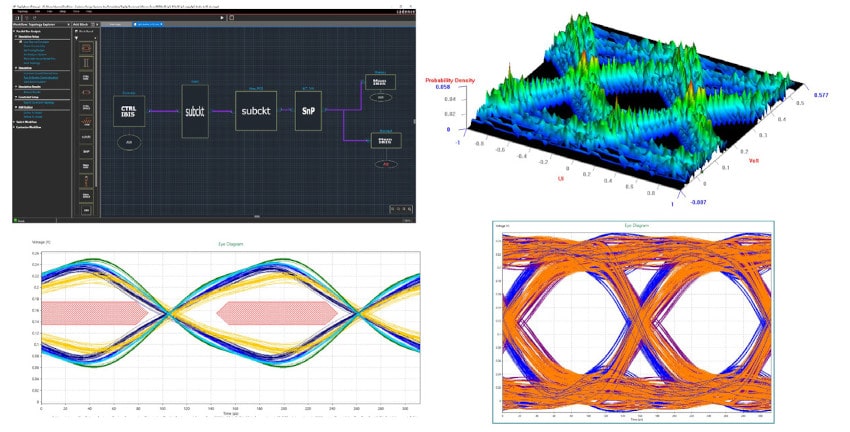

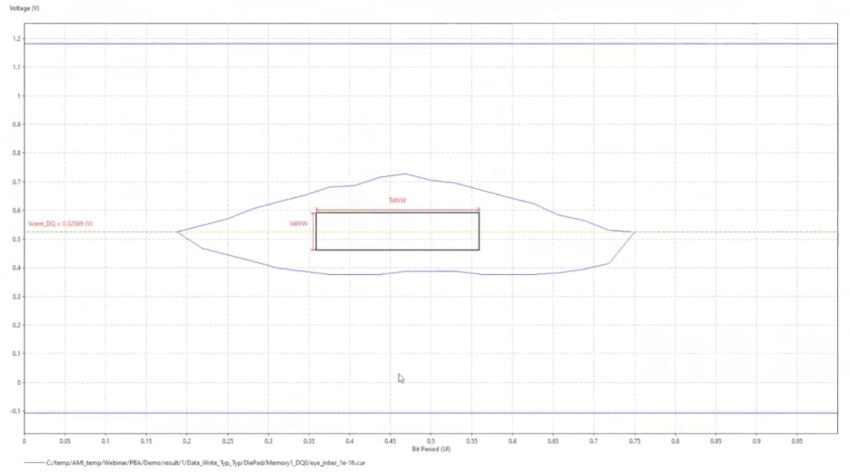

DDR5 simulations and data-dependent measurements are done with Sigrity X by using accurate interconnect models, plus accurate modeling of transceiver equalization.

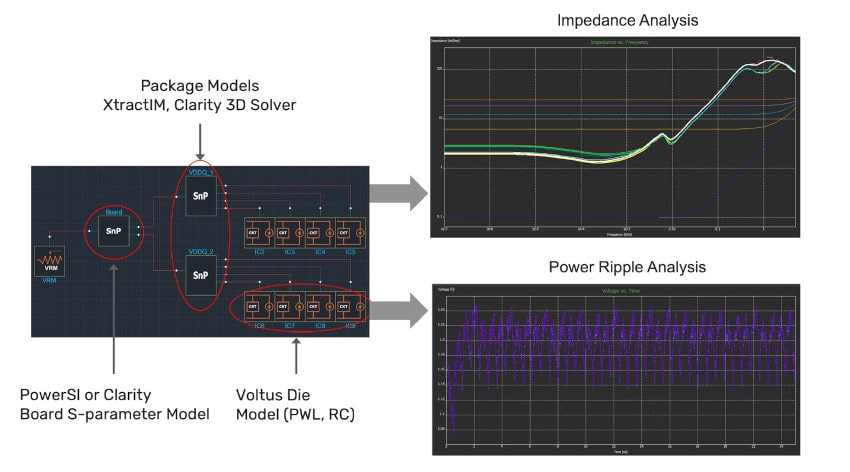

Analyzing a board and package power delivery network (PDN) is accomplished using Sigrity, Clarity 3D Solver and Voltus IC Power integrity in a flow.

Case Studies

Setting up a Sigrity Simulation starts with dragging and dropping a .brd file into the window, then selecting which nets should be simulated. Ports are generated based on the selected nets, then compute resources are selected.

Continuing the DDR example a testbench is created, a circuit simulator selected, then time domain results viewed. A channel report is run and the results are compared versus expected, based on the standard, so this mask is passing at 4.4Gbps.

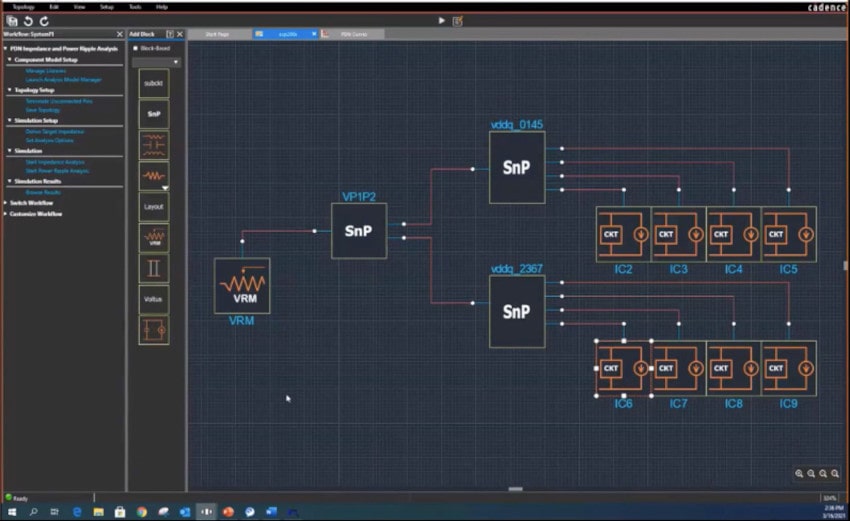

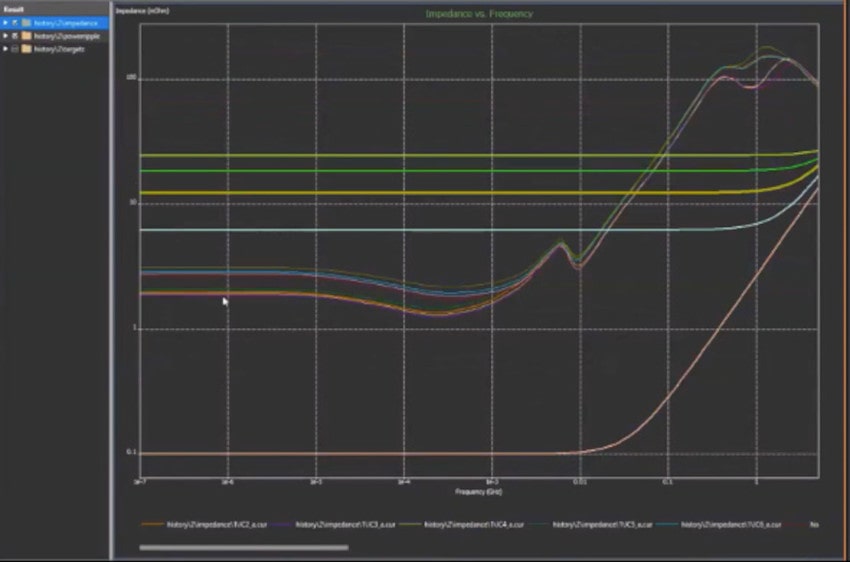

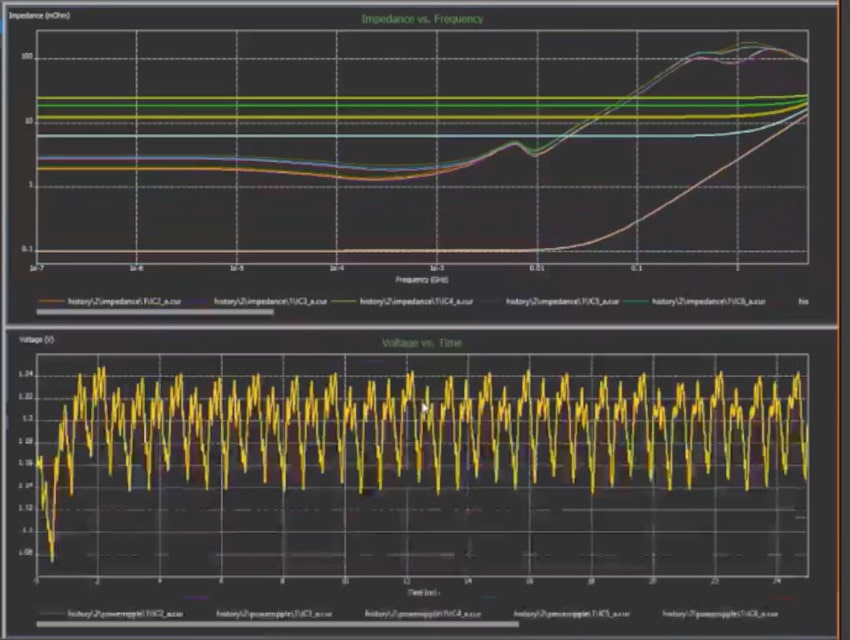

A power domain analysis was run on a system consisting of building blocks, subcircuits, S-parameter blocks, ideal elements, layout element, VRMs, Voltus blocks, plus an IC block. The IC block has a PWL source for the current. Target impedance is then simulated. Impedance from all eight nodes (IC2:IC9) is examined and compared to the target impedances.

Some of the eight impedances are peaking out above 100MHz, so the designers can reduce these impedances to meet the power ripple specification.

A final simulation is run after impedance changes, then the eight nodes are examined and the ripples are overlapping each other. Both impedance and power ripple results have been analyzed properly at the system-level.

Summary

SI/PI analysis is improved by the abilities in Sigrity X and the Clarity 3D Solver, using distributed simulation. Your PCB and IC package design teams will have increased confidence that each new project will meet requirements through SI/PI analysis.

Read the complete 18-page White Paper on Sigrity X.

Related Blogs

Share this post via: