Cách cập nhật thiết bị FPGA của bạn với Questa

It’s a fact of life that technology marches on. Older process nodes get replaced by newer ones. As a result, ASSPs and FPGAs are obsoleted, leaving behind large system design investments that need to re-done. Since many of these obsolete designs are performing well in the target application, this re-do task can be particularly vexing. Thanks to advanced technology offered by Siemens Digital Industries Software, there is now another way around this problem. Using the Questa™ Equivalent FPGA retargeting flow, all the work on obsolete designs no longer needs to go to waste. Siemens recently published a white paper that takes you through the entire process. A link is coming, but first let’s look at the big picture and how to update your FPGA devices with Questa.

An Overview of the Problem and the Flow

The goal of the flow presented in the white paper is to extend the design life of obsolete FPGAs by migrating those designs to newer technologies. This way, the design work can be reused with the added benefit of taking advantage of the latest safety, security, and power saving features of newer FPGAs. The fundamental (and correct) premise here is that retargeting a working design to a newer technology takes far less time and effort than re-designing the application from scratch. Siemen’s Questa Equivalent FPGA retargeting solution is at the center of this approach.

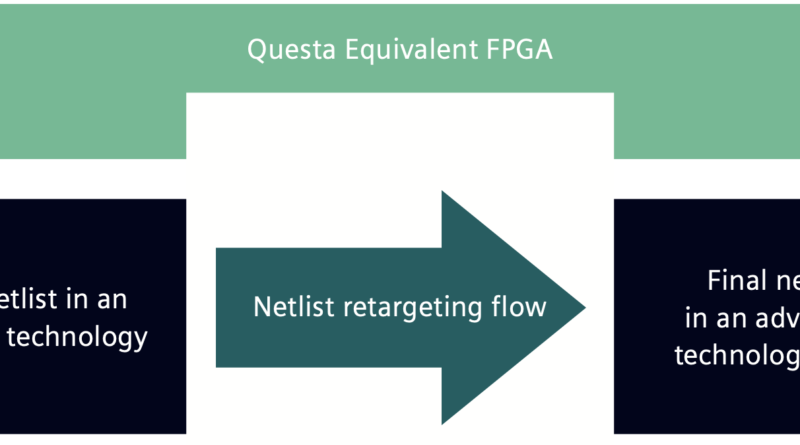

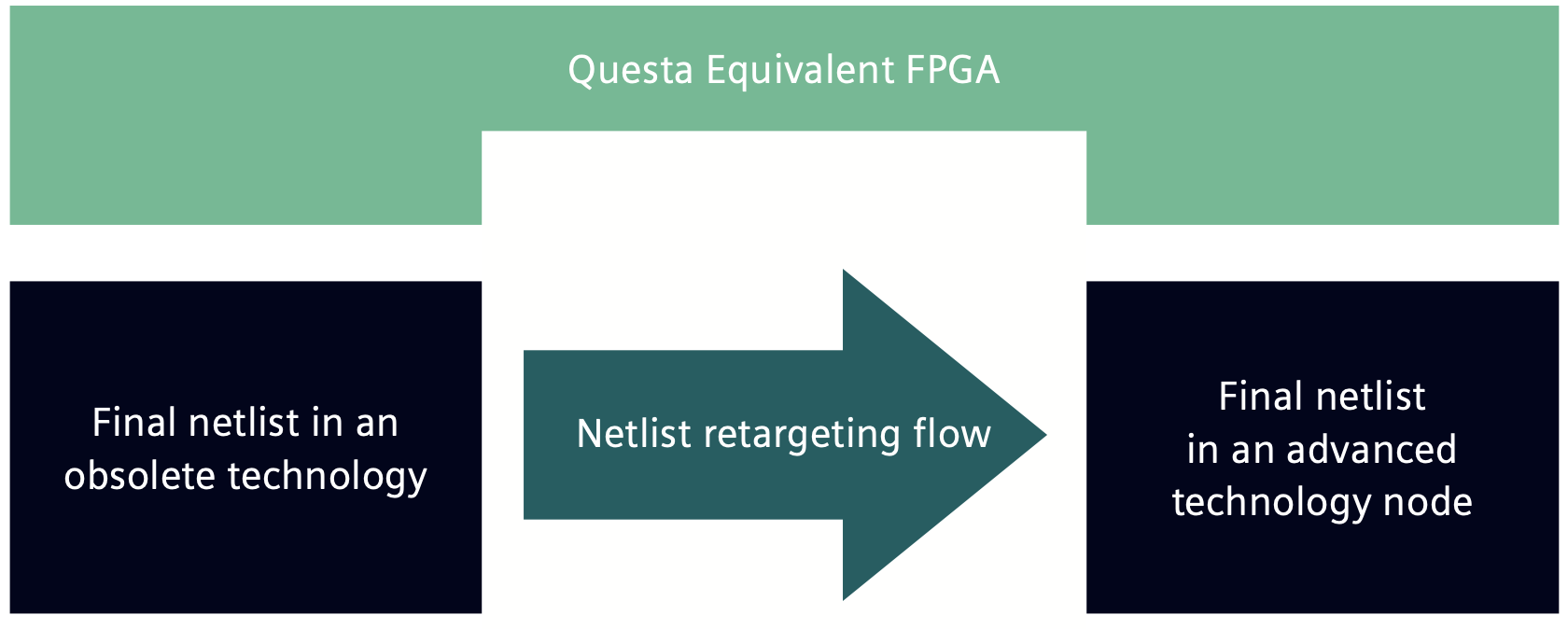

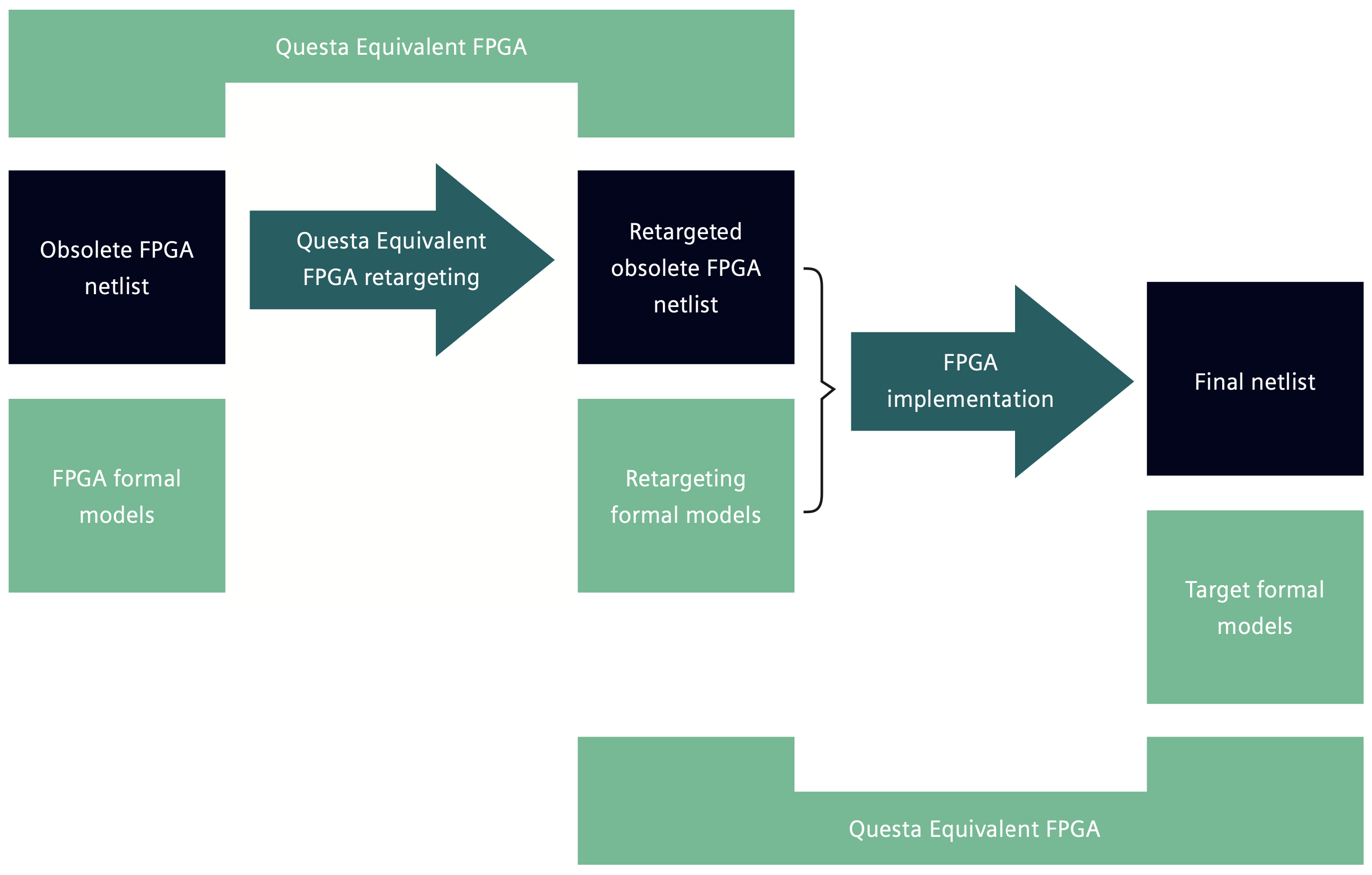

Additional motivation includes process simplification and cost reduction due to end-of-life supply limitations and minimization of counterfeit risks that may be present in older supply chains. The proposed solution takes the final netlist from the original design and generates a functionally equivalent final netlist in a modern target FPGA technology. Months of engineering time can be eliminated because designers do not have to recreate the RTL for reimplementation on a modern FPGA device.

A high-level view of this process is shown in the graphic at the top of this post. Digging a bit deeper, the figure below provides more details of the retargeting methodology presented in the white paper.

Details of Use Cases

Not all design situations are the same. Recognizing that, the Siemens white paper presents three use cases. You will get all the information needed to build your migration strategy in the white paper – again, a link is coming. For now, let’s briefly examine the three scenarios that are discussed.

Use Case 1: Equivalence with RTL: In addition to proving the obsolete netlist against the new netlist, Questa Equivalent FPGA can be used to prove the functional equivalence of the RTL to the obsolete netlist, if it has not been manually modified to meet the requirements of the original specification. A complete description of how to examine the design to identify any needed additional inputs and how to set up this flow are all covered.

Use Case 2: RTL Retargeting: If the RTL is available for the obsolete device netlist and you decide to use the RTL for synthesis and retargeting and want to verify the old device netlist versus the new netlist (synthesized using RTL), this is the flow to use.

A high-level summary of this flow includes:

- Synthesize the RTL for the new device

- Create (if necessary) and apply formal models for the new device netlist

- Prove functional equivalence for RTL versus the new device netlist using Questa Equivalent FPGA

- Create (if necessary) and apply formal models for the obsolete device netlist

- Prove functional equivalence of the obsolete device netlist versus the modern device netlist using Questa Equivalent FPGA

Again, all the details about how to examine the design and identify any needed information and how to set up the overall flow are covered in the white paper.

Use Case 3: RTL-RTL Retargeting: RTL-RTL retargeting can be used if the RTL of the obsolete device netlist has IP that is no longer available for the new device, and the obsolete IP can be replaced with up-to-date IP with similar functionality (or functionally equivalent logic).

A high-level summary of this flow includes:

- Replace the obsolete IP with similar updated IP or equivalent logic

- Create (if necessary) and apply formal models for the obsolete device IP

- Create (if necessary) and apply formal models for the new device IP

- Prove functional equivalence for RTL with obsolete IP versus RTL with updated IP (or equivalent logic) using Questa Equivalent FPGA

- Synthesize the RTL for the new device

- Create (if necessary) and apply formal models for the new device netlist

- Prove functional equivalence for RTL with updated IP or equivalent logic versus the new device netlist using Questa Equivalent FPGA

- Create (if necessary) and apply formal models for the obsolete device netlist

- Prove functional equivalence for RTL with obsolete IP versus the obsolete device netlist using Questa Equivalent FPGA

As before, all the details of how to examine the design to identify missing data, how to create that data, and how to set up the flow are all covered in the white paper.

To Learn More

In most cases, reuse makes more sense than redesign. If you are faced with this decision, I highly recommend you find out how Siemens Digital Industries Software can help. You can download the Questa Equivalent FPGA Retargeting Flow white paper here. And that’s how to update your FPGA devices with Questa.

Also Read:

The RISC-V and Open-Source Functional Verification Challenge

Prioritize Short Isolation for Faster SoC Verification

Navigating Resistance Extraction for the Unconventional Shapes of Modern IC Designs

Share this post via: