Breker nâng khả năng xác minh RISC-V lên một tầm cao mới #61DAC

RISC-V is clearly gaining momentum across many applications. That was quite clear at #61DAC as well. Breker Verification Systems solves challenges across the functional verification process for large, complex semiconductors. Its Trek family of products is production-proven at many leading semiconductor companies worldwide. So, it seems logical that Breker brings RISC-V verification to the next level and that’s exactly what the company did at #61DAC.

The highlight of Breker’s presence at the show includes:

- A complete range of tests for the entire RISC-V core verification stack from ISA to system-level interaction and performance.

- Test Suite Synthesis AI Technology to track complex, unpredictable bugs and accelerate coverage of complex, super-scalar, out-of-order microarchitecture pipeline implementations

- Self-checking content that is portable across simulation, emulation, and post silicon with debug and coverage analysis

Let’s look at how Breker brings RISC-V verification to the next level.

RISC-V Automated Core Verification with Synthesis Amplification

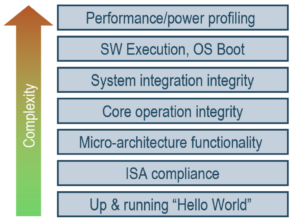

The verification of a RISC-V processor core should include a “stack” of scenarios as shown in the figure. Breker’s RISC-V CoreAssurance SystemVIP uniquely provides this complete scenario range. A complete range of tests for the entire RISC-V core verification stack is provided. Starting with randomized instruction generation and microarchitectural scenarios, unique tests are provided that check all integrity levels, ensuring the smooth application of the core into an SoC.

This can also be extended to allow custom RISC-V instructions to be fully incorporated into the complete test suite. The capability may be ported across simulation, emulation, prototyping, post-silicon, and virtual platform environments to complete the picture.

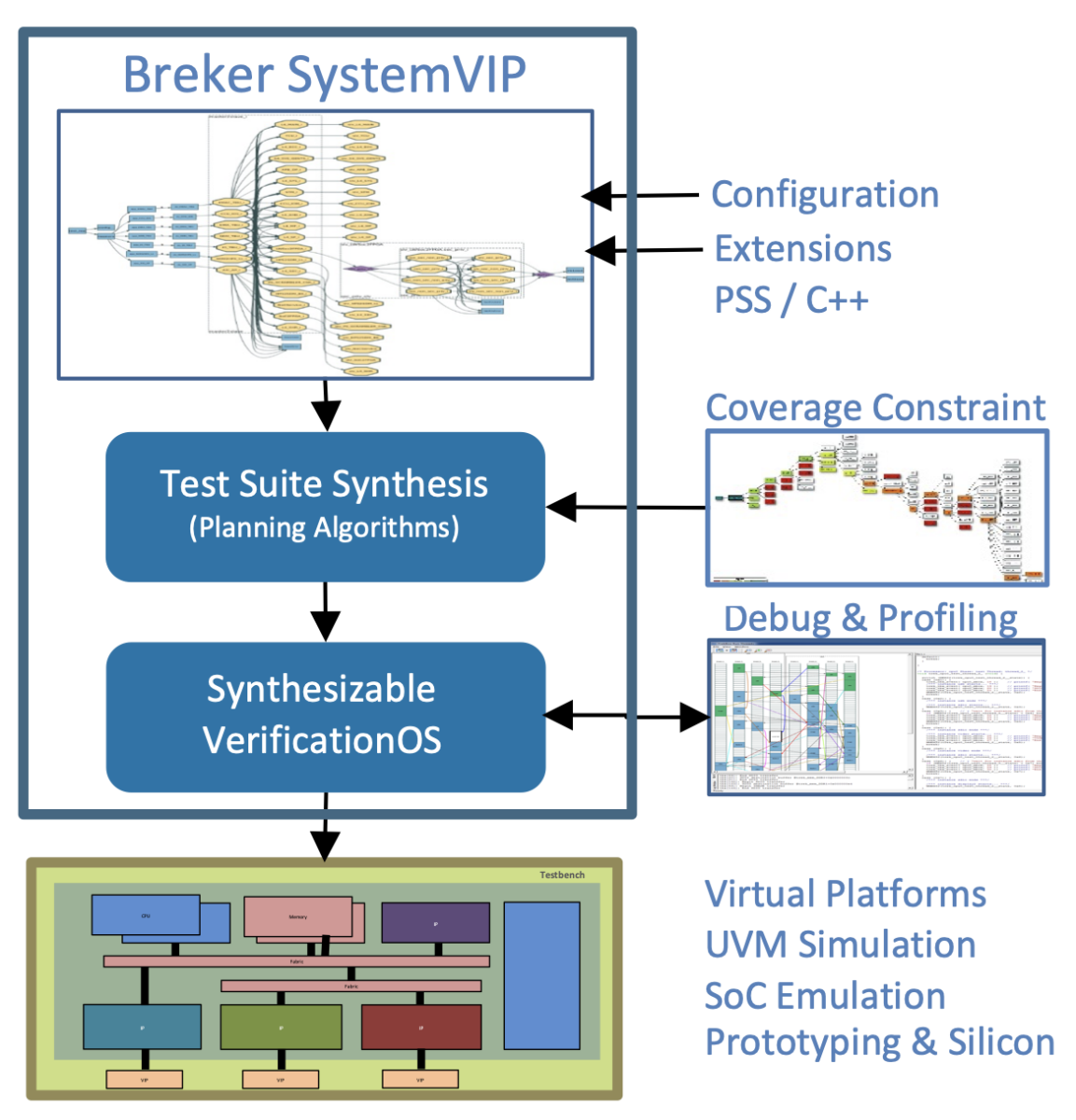

A capability called test suite synthesis verification amplification is also included. Most test suites are templated in nature, allowing individual tests to be configured for various design situations. Using Planning Algorithms, an AI technique, Breker’s SystemVIP is based on synthesis technology that has an amplifying effect on the scenario models to significantly improve coverage and bug hunting.

Comprehensive System Coherency Verification

Breker’s popular Cache Coherency SystemVIP is used by most of the leading semiconductor companies worldwide to find hundreds of bugs over many complex SoCs. As the complexity of SoCs increases, so does the requirement for system level coherency that includes fabric and I/O, as well as advanced memory architectures.

Breker addresses these challenges with its next generation System Coherency SystemVIP, leveraging Test Suite Synthesis to generate a broad range of coherency tests. These tests are based on multiple verification algorithms and may be easily configured to operate on all memory and fabric architectures across multicore platforms. The synthesis platform includes AI planning algorithms, cross combination and concurrent scheduling for high-coverage, and complex corner-case evaluation.

As more complex RISC-V multi-cores and systems are produced, coherency for these designs is increasing in importance. Breker’s coherency SystemVIP works hand-in-hand with its other RISC-V SystemVIPs to enable a complete solution for the most advanced designs.

The SystemVIP can generate both C code and transactions for SoC testbenches, or UVM sequences for cache unit and sub-system simulation. It can operate on a virtual prototype, simulation, emulation, FPGA prototype and even actual silicon platforms, and includes full debug and profiling of the device under test on those platforms.

Breker’s Test Suite Synthesis has been shown to produce dramatic improvements in test composition time and coverage over and above basic test generators, including typical templating test schemes. The figure below provides an overview of the platform.

The CEO Perspective

I had the opportunity to catch up with my good friend and CEO at Breker, Dave Kelf. I wanted to get his perspective on RISC-V market and the impact these new innovations from Breker are having. Here’s what Dave had to say:

While RISC-V represents a huge discontinuity across the electronic industry, there is a quality expectation that has been set by companies such as Arm that RISC-V cores must meet to be successful. This requires in-depth, comprehensive verification, and the best way to meet at least part of this need is to reuse test suites that are already proven.

RISC-V verification has its unique challenges, and these are compounding as the cores get more advanced. Existing, templated tests are fine for basic embedded cores, but run out of steam for the types of devices that are now emerging. We need to apply synthesis techniques to tease out deep sequential, unpredictable bugs, implement performance-based testing and enable system-level integration verification, and this accounts for the demand explosion we have seen at Breker.

To Learn More

You can learn more about RISC-V automated core verification with synthesis amplification here and you can learn more about comprehensive system coherency verification here. And that’s how Breker brings RISC-V verification to the next level at #61DAC.

Share this post via: