2024 Thiết lập sân khấu cho những đổi mới liên kết NoC trong thiết kế SoC

What a year it’s been for Arteris! Reflecting on 2024, the company achieved exciting milestones and breakthroughs that pushed the boundaries of system-on-chip (SoC) design. A game-changing new technology was unveiled, a major product was launched, and existing solutions were tailored for AI, automotive, high-performance computing (HPC) and more.

Along the way, we welcomed new partners and deepened relationships with existing ones, strengthening collaborations that drive progress. By staying closely connected with customers, our engineers delivered practical solutions to address the ever-evolving challenges of modern SoC design.

Ecosystem expansion

Partnerships were a highlight of 2024, showcasing Arteris’ reach across the semiconductor ecosystem. Among the many relationships the company cultivated, we strengthened ties with IP providers like Andes Technology, MIPS and SiFive, worked with chipmakers such as Tenstorrent, EdgeQ and Rain AI, and expanded our partnership with Arm. Support for VeriSilicon with its one-stop custom silicon services also continued to grow. These examples represent just a portion of the partnerships driving innovation and progress across our industry as we remain committed to advancing RISC-V, AI, edge computing, and SoC design success.

Technology advancements

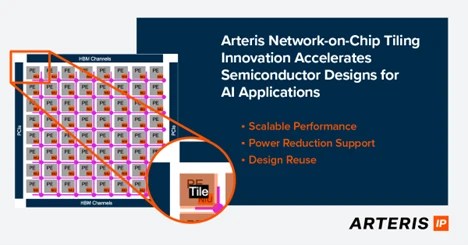

This year, groundbreaking NoC soft tiling capabilities were introduced within Arteris’ FlexNoC and Ncore interconnect IPs. This transformative approach enables SoC architects to partition chips into modular, self-contained units, allowing seamless scaling of compute performance to meet evolving demands. An additional benefit is its support for derivative design, which allows pre-verified soft tiles to be reused across multiple SoCs, significantly reducing development time. In some cases, this approach has achieved up to a 50% reduction.

Soft tiling can also deliver up to 20% energy savings by selectively deactivating tiles when not in use, minimizing power consumption. Beyond efficiency, this modular methodology accelerates time to market, reduces design risks and ensures high yields in advanced node manufacturing. With NoC soft tiling, we enable SoC architects to achieve high levels of performance and efficiency while meeting the demands of today’s applications.

Explore this Semiconductor Engineering article on Scaling AI Chip Design With NoC Soft Tiling.

Product enhancements

Cache Coherent Interconnect IP

In 2024, we enhanced our Ncore Cache Coherent Interconnect IP to work with multiple processor IPs, including RISC-V and Arm architectures. Ncore ensures data consistency across CPUs, GPUs and accelerators, reducing software complexity and streamlining memory management. Its flexible architecture supports configurations ranging from fully coherent to non-coherent and IO-coherent interfaces, making it ideal for markets like automotive, enterprise computing and safety-critical systems.

Designed for maximum productivity, Ncore accelerates time to market by streamlining the connection of semiconductor IP blocks. It’s also functionally safe, meeting ISO 26262 ASIL B through D standards. The interconnect IP has saved design teams up to 50 years of engineering effort per project compared to manual interconnect solutions.

Check out the video with Ed Sperling and Andy Nightingale on Cache Coherency In Heterogeneous Systems.

Last-level cache IP

While much of 2024 focused on new launches, the engineering team at Arteris also worked to enhance existing technologies. CodaCache, our advanced last-level cache (LLC) IP solution, continues to tackle the challenges of efficient memory management. With a flexible architecture that supports various operational modes, CodaCache optimizes data throughput and energy efficiency, reducing latency and boosting performance in high-demand applications like AI inference and real-time processing.

See how to Turbocharge Cost-Conscious SoCs With Cache in this Semiconductor Engineering article by John Min.

Hardware/software integration

Hardware/software integration remains a challenge, and Arteris has been hard at work addressing it. CSRCompiler and Magillem Registers are two software products that tackle the HSI challenges design teams face today. These tools streamline IP block management and automate hardware/software interface generation, reducing errors by 30%+ and accelerating development cycles from multiple weeks to hours. Practical approaches like these help engineers keep projects on schedule and within budget.

Uncover the Promises And Pitfalls Of SoC Restructuring in this Semiconductor Engineering video with Ed Sperling and Tim Schneider.

Looking ahead

The achievements of 2024 highlight Arteris’ leadership in system IP including SoC interconnect IP and integration automation software. Advancements in modular scaling, cache and non-cache coherence, multi-protocol support, memory optimization and hardware/software integration position the company to enable engineers to develop the latest innovations for AI, automotive, data centers and other markets where efficiency, performance and scalability are required.

As we look ahead to 2025, our continuous drive for innovation is unstoppable. Stay tuned!

Andy Nightingale

Andy Nightingale is vice president of product management and marketing at Arteris. He has more than 36 years of experience in the high-tech industry, including 23 years in various engineering and product management positions at Arm.