Làm Chủ Đồng TSV Điền Phần 1/3

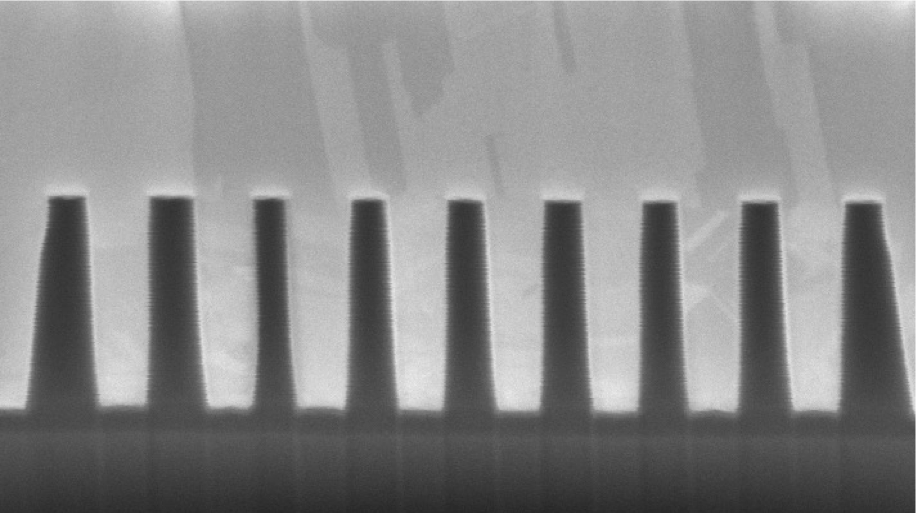

Establishing void-free fill of high aspect ratio TSVs, capped by a thin and uniform bulk layer optimized for removal by CMP, means fully optimizing each of a series of critical phases. As we will see in this 3-part series, the conditions governing outcomes for each phase vary greatly, and the complexity of interacting factors means that starting from scratch poses an empirical pursuit that is expensive and of long duration.

Robust and void-free filling of TSVs with copper progresses through six phases as laid out below:

- Feature wetting and wafer entry

- Feature polarization

- Nucleation

- Fill propagation

- Accelerator ejection

- Bulk layer plating

- (Rinsing and drying, which we won’t cover in this series)

Feature wetting

The primary purpose of the feature wetting step is, well, not very mysterious. It is to fully wet the wafer surface and most especially the features themselves. Inadequate feature wetting leads to trapping of air inside the TSV. That trapped air impedes plating, causing voids.

Wetting is by no means trivial, and the difficulty of fully wetting features increases dramatically with aspect ratio. There is a process window based on time of exposure of the features to the water. Too little time allowed for wetting will lead to incomplete wetting and bubbles (thus, voids). However, too much time for wetting will result in corrosion of the copper seed (thus other voids).

Side note: One of the biggest challenges in copper TSV formation actually comes before the copper fill step. I’m talking about the contiguous coverage of the feature in PVD copper seed. You probably guessed that the degree of difficulty in proper seed deposition increases dramatically with aspect ratio. Oh, how right you are. Getting good seed coverage in higher aspect ratio vias tends to require both sophisticated PVD systems and sophisticated PVD process engineers (neither of which comes cheap). The toughest spot to cover is the lower portion of the sidewall immediately adjacent to the via floor. If feature wetting is not optimized, seed corrosion can occur, exposing the underlying barrier and preventing plating altogether in that area, resulting in…voids. If you have non-optimized wetting that results in corrosion, the bottom of the via wall is where you are sure to see it.

Let’s talk methods of wetting. I’m sure there are exceptions but, generally speaking, wetting of TSV features is done in deionized water (DI). The wetting step can be accomplished using one of several different methods. I briefly summarize the most common methods below, along with the pros and cons of each:

Immersion wetting:

- What is it: Simply immersing a dry wafer into a prewet bath.

- Pros: Hardware requirements are minimal, amounting only to immersing the wafer into a pool of water.

- Cons: This is the least aggressive method and is unlikely to work on vias of even modest aspect ratio. Even though the seed copper is highly hydrophilic, at this scale, wetting can proceed very slowly due to simple air entrapment or minor disadvantage in surface energy.

Spray wetting:

- What is it: Spraying of water against the surface of the spinning wafer.

- Pros: Spray is a quite effective way to completely wet features due to the more aggressive exchange of water at the surface which more effectively disrupts air entrapment.

- Cons: Above an aspect ratio of around 5:1, spray wetting may be too slow to be effective, depending on the sensitivity of the TSV sidewall copper seed. Hardware complexity is higher than immersion and may not be available on the plating system you use. Wet transfer from a spray wetting system to a plating system is possible.

Vacuum Prewet:

- Wetting of the wafer in a vacuum, then venting to atmosphere to drive water into the features.

- Pros: Vacuum prewet is a highly effective and fast way to fully wet even TSVs of aspect ratio 10:1 and greater.

- Cons: Most systems do not offer a vacuum prewet chamber. Even with access to vacuum prewet, recipe structure and settings must be optimized to avoid process issues; for example, excessive vacuum can lead to ambient pressure boiling of the water.

One last point on wetting, treatment of the water stream can help significantly to reduce (or nearly eliminate) corrosion rate, drastically opening process window. This improvement could be critical if seed copper is particularly thin, which is common at the base of the via sidewall in higher aspect ratio features.

Also, you have noticed I keep saying, “voids.” You want to master TSV? Master elimination of voids.

Once the wafer is wetted, it must be transferred to the plating reactor. The transfer of the wafer should be accomplished quickly to avoid evaporation of water on the wafer. Generally, the water inside the features will not evaporate quickly, however, water can evaporate quickly from the wafer surface, causing surface corrosion.

Wafer Entry

Immersion of the wafer into the plating fluid is the next consideration. Most state of the art plating systems introduce the wafer into fluid with the feature side facing down. Platers of this type are commonly called, “fountain platers,” because the chemistry flows continually upward and over a weir, replicating the behavior of a fountain. The other common plating chamber type uses a vertical orientation of the wafer. Systems of this type are often called “rack platers.”

Immersion of a wafer in a vertical orientation is typically straightforward, the primary risk being the trapping of air in and around the hardware features of the wafer holder. Immersion of a wafer into a fountain plater is comparatively more complex due to the need to evacuate air from under the wafer during immersion. This step is commonly called, “wafer entry,” and involves careful tilting of the wafer to a specific angle, at an optimal wafer rotational rate, and vertical downward velocity in order to prevent trapping of air against the wafer surface that leads to major…wait for it…voids.

Given the relatively higher complexity of wafer immersion in fountain plater systems, one may be tempted to think that vertical platers represent a preferable architecture, but they do not. For reasons I’ll share in a future post, the magic of rotating submerged disc physics makes fountain platers the industry’s best plating reactors.

Also Read:

Nvidia Sells while Intel Tells

Share this post via: