Công cụ EDA mới để phân tích nhiệt 3D

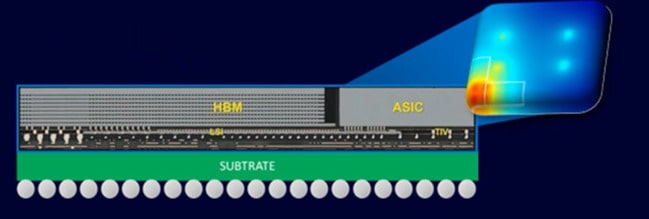

An emerging trend with IC design is the growing use of chiplets and even 3D IC designs, as the disaggregated approach has some economic and performance benefits over a single SoC. There are thermal challenges with using chiplets and 3D IC designs, so that means that thermal analysis has become more important. I just spoke with Michael White, Sr. Director in the Calibre group at Siemens EDA to get an update on their newest product, and it’s called Calibre 3DThermal.

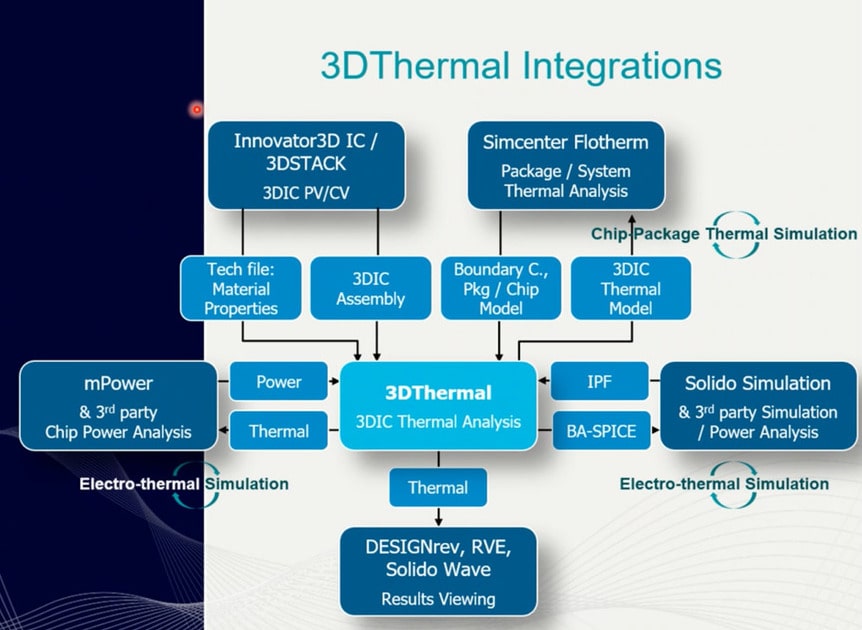

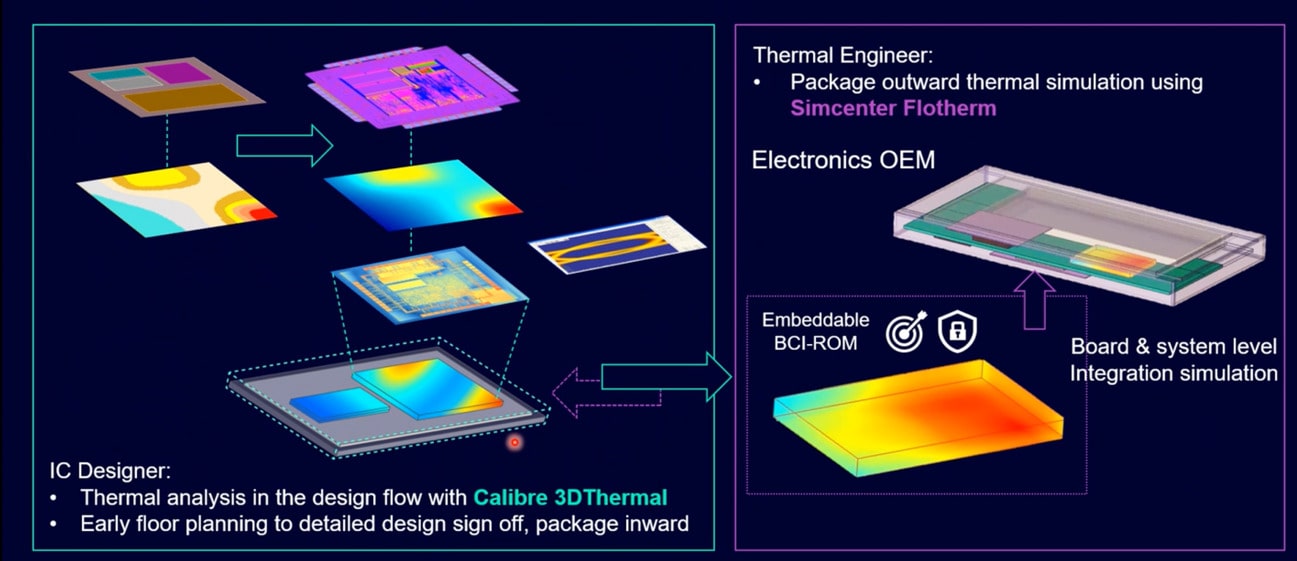

The emphasis with Calibre 3DThermal is to enable shift-left, helping IC designers get through analysis and verification more efficiently by doing early feasibility analysis of their IP, chiplet, SoC and package, eliminating surprises at the end of a project. This approach allows a team to start thermal analysis quite early, even in the concept phase with very few details, just to get the analysis process started. Siemens EDA has an array of tools from IC to package to systems, and now these tools can communicate through thermal analysis.

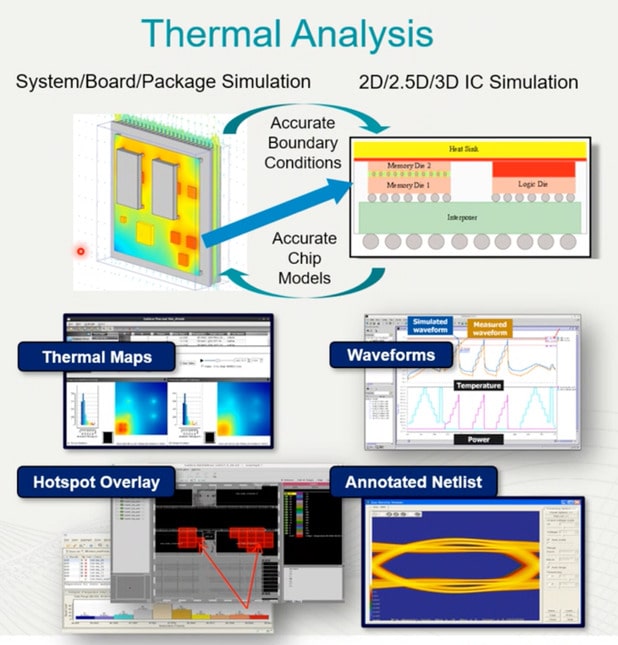

This is another example of EDA enabling multi-physics analysis, as thermal issues also impact power, stress, timing and variation. Calibre 3DThermal has been designed to be easy to learn and use. The Simcenter Flotherm tool has been in use for years now in package and system thermal analysis, and with 3DThermal design teams can pass info back and forth from inside the package then outwards to the system. As a design progresses and more details are available, then annotated SPICE netlists are sent to Solido and other circuit simulators.

Early feasibility analysis helps design teams make decisions about floor planning, gauging the impact of using heatsinks, adding thermal TSVs, and seeing how close they are at meeting power, thermal and timing goals. Data used in Flotherm can use an embedded, abstracted model of the package, even encrypting it to hide any sensitive details or trade secrets.

.

Inside the 3DThermal tool is an optimized version of the Flotherm solver for even better capacity during analysis of large IC designs. The 3DThermal tool could be used by a package engineer, systems designer or an IC designer to perform analysis. Engineers add details like LEF/DEF and GDS/OASIS files. Fast and accurate results are made easier through automatic gridding, automatic time step generation and automatic chip thermal model creation. The 3Dblox language started by TSMC is also supported.

UMC and their customers collaborated with Siemens EDA during the development of Calibre 3DThermal

Summary

It’s a busy week at DAC, and Siemens EDA has just announced another addition to the growing Calibre family of tools with their new 3DThermal product, enabling chiplet and 3D IC designers to start early thermal analysis, then proceed throughout the design process to work with package and systems engineers to meet thermal, power and timing goals. Multi-physics analysis is enabled with this approach, allowing teams to shift-left on tough problems. Expect to see announcements from the major foundries on their support of Calibre 3DThermal.

Read the press release from Siemens EDA online.

Related Blogs

Share this post via: